# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

# MC3419-1L

#### **TELEPHONE LINE-FEED CIRCUIT**

... designed as the heart of a circuit to provide BORSHT functions for telephone service in Central Office, PABX, and Subscriber Carrier equipment. This circuit provides dc power for the telephone (Battery), Overvoltage protection, Supervision features such as hook status and dial pulsing, two-wire differential to four-wire single-ended conversions and suppression of longitudinal signals at the two-wire input (Hybrid), and facilitates ringing insertion, Ring trip detection and Testing.

- Totally Upward Compatible with the MC3419

- All Key Parameters Externally Programmable

- Current Sensing Outputs Monitor Status of Both Tip and Ring Leads for Auxiliary Functions such as: Ground Key, Ring Trip, Message Waiting Lamp, etc.

- On-Hook Power Below 5.0 mW

- Digital Hook Status Output

- Powerdown Input

- Ground Fault Protection

- Operates from Single -20 V to -56 V Power Source

- Size and Weight Reduction Over Conventional Approaches

- The sale of this product is licensed under Patent No. 4,004,109.

All royalties related to this patent are included in the unit price.

# SUBSCRIBER LOOP INTERFACE CIRCUIT (SLIC)

BIPOLAR LASER-TRIMMED INTEGRATED CIRCUIT

L SUFFIX CERAMIC PACKAGE CASE 726-04

MAXIMUM RATINGS (Voltages Referenced to V<sub>CC</sub>.)

|                                                    |                                    | <del>, ·</del>                |      |

|----------------------------------------------------|------------------------------------|-------------------------------|------|

| Rating                                             | Symbol                             | Value                         | Unit |

| Voltage                                            | V <sub>EE</sub><br>V <sub>QB</sub> | -60<br>V <sub>EE</sub> -1.0 V | Vdc  |

| Powerdown Input Voltage Range                      | V <del>PDI</del>                   | + 15 to - 15                  | Vdc  |

| Sense Current<br>Steady State<br>Pulse — Figure 4  | ITSI, IRSI                         | 100<br>200                    | mAdc |

| Storage Temperature Range                          | τ <sub>stg</sub>                   | -65 to +150                   | °C   |

| Operating Junction Temperature (θJA = 100°C/W Typ) | TJ                                 | 150                           | °C   |

# **OPERATING CONDITIONS** (Voltages Referenced to $V_{CC}$ .)

| Rating                                                           | Symbol                              | Value                    | Unit |

|------------------------------------------------------------------|-------------------------------------|--------------------------|------|

| Operating Ambient Temperature Range                              | ТА                                  | 0 to +70                 | °C   |

| Loop Current                                                     | IL                                  | 10 to 120                | mA   |

| Voltage                                                          | V <sub>EE</sub><br>V <sub>QB</sub>  | -20 to -56<br>-20 to VEE | Vdc  |

| Analog Ground<br>( $I_L = 0$ to 60 mA)<br>( $I_L = 0$ to 120 mA) | VAG                                 | 0 to -12<br>-2.5 to -12  | Vdc  |

| Supervisory Output Voltage<br>Compliance Range                   | V <sub>RSO</sub> , V <sub>TSO</sub> | -2.0 to -20              | Vdc  |

| Hook Status Output                                               | VHSO                                | + 15 to - 20             | Vdc  |

| Loop Resistance                                                  | RL                                  | 0 to 2500                | Ω    |

# **TRANSMISSION CHARACTERISTICS** (R<sub>L</sub> = 600 $\Omega$ unless otherwise noted.)

| Characteristic                                                                                                                 | Figure | Symbol                                                               | Min            | Тур          | Max            | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------|----------------|--------------|----------------|------|

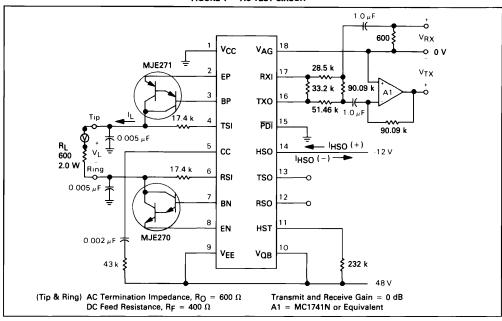

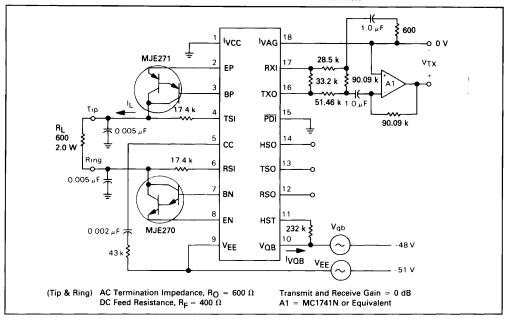

| Transmit and Receive Gain Variation<br>(Insertion Loss)<br>(1.0 kHz @ 0 dBm Input)                                             | 1      | V <sub>TX</sub> /V <sub>L</sub> ,<br>V <sub>L</sub> /V <sub>RX</sub> | -0.3           | 0            | +0.3           | dB   |

| Transhybrid Rejection<br>(Input — 1.0 kHz @ 0 dBm)<br>Fixed (1%) Resistor Balance Network<br>Trimmed Balance Network All Types | 1      | VTX/VRX                                                              | - 23<br>       | - 35<br>- 55 | _              | dB   |

| Level Linearity ( -48 to +3.0 dBm, referenced to 0 dBm @ 1.0 kHz) Transmission Reception                                       | 1      | V <sub>TX</sub> /V <sub>L</sub><br>V <sub>L</sub> /V <sub>RX</sub>   | - 0.1<br>- 0.1 | 0            | + 0.1<br>+ 0.1 | dB   |

| Frequency Response (200-3400 Hz referenced to 1.0 kHz @ 0 dBm) Transmission Reception                                          | 1      | V <sub>TX</sub> /V <sub>L</sub><br>V <sub>L</sub> /V <sub>RX</sub>   | - 0.1<br>- 0.1 | 0            | + 0.1<br>+ 0.1 | dB   |

| Total Distortion @ 1.0 kHz, 0 dBm<br>(C-Message Filtered)                                                                      | 1      | V <sub>L</sub> /V <sub>RX</sub><br>V <sub>TX</sub> /V <sub>L</sub>   | _              | - 60<br>- 60 | _              | dB   |

# TRANSMISSION CHARACTERISTICS (continued) (RL = 600 $\Omega$ unless otherwise noted.)

| Characteristic                                        | Figure | Symbol                                                                  | Min  | Тур | Max | Unit  |

|-------------------------------------------------------|--------|-------------------------------------------------------------------------|------|-----|-----|-------|

| Idle Channel Noise (V <sub>RX</sub> = 0 V)            | 1      | V <sub>TX</sub> , V <sub>L</sub>                                        | _    | 3.0 | 10  | dBrnC |

| Return Loss (referenced to 600 ohms) @ 1.0 kHz, 0 dBm | 1      | $20 \text{ Log } \left  \frac{R_0 - 600}{R_0 + 600} \right $            | 30   |     |     | dB    |

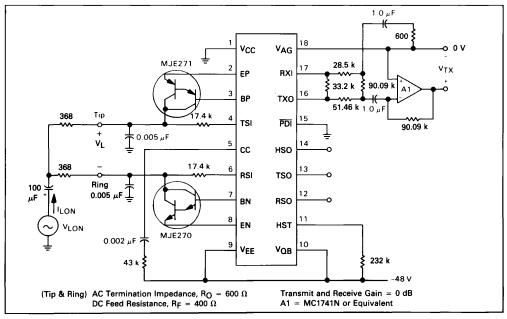

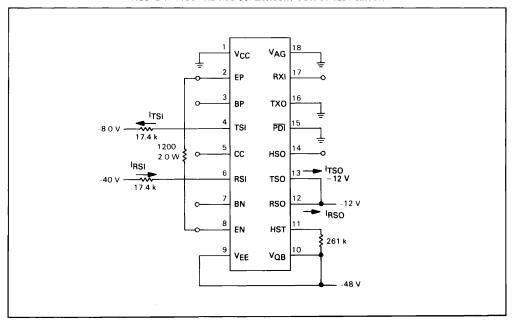

| Longitudinal Induction (60 Hz)<br>(ILON = 35 mA RMS)  | 2      | V <sub>TX</sub>                                                         |      | 5.0 | _   | dBrnC |

| Longitudinal Balance (200–3000 Hz)                    | 2      | V <sub>TX</sub> /V <sub>LON</sub> ,<br>V <sub>I</sub> /V <sub>LON</sub> | - 45 | _   |     | dB    |

# **ELECTRICAL CHARACTERISTICS** (V<sub>EE</sub> = -48 V, V<sub>QB</sub> = V<sub>EE</sub>, V<sub>AG</sub> = 0 V, R<sub>L</sub> = 600 $\Omega$ , T<sub>A</sub> = $25^{\circ}$ C unless otherwise noted.)

| Characteristic                                                                                                                                                                                                                                             | Figure | Symbol                                                                                   | Min                 | Тур                    | Max               | Unit                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------|---------------------|------------------------|-------------------|----------------------|

| Propagation Delay                                                                                                                                                                                                                                          | 1      | T <sub>P</sub> , V <sub>RX</sub> to V <sub>L</sub><br>V <sub>RX</sub> to I <sub>TX</sub> | _                   | 750<br>1.2             | _                 | ns<br>μs             |

| Supply Current — On-Hook<br>(VEE = VQB = 56 V, R <sub>L</sub> > 100 MΩ)                                                                                                                                                                                    | 3      | lvcc                                                                                     | _                   | 40                     | 200               | μΑ                   |

| On-Hook Power Dissipation (R <sub>L</sub> > 100 M $\Omega$ )                                                                                                                                                                                               | 3      | PD                                                                                       | -                   | 1.0                    | _                 | mW                   |

| Power Supply Noise Rejection<br>(1.0 kHz @ 1.0 V <sub>RMS</sub> )                                                                                                                                                                                          | 3      | V <sub>TX</sub> /V <sub>ee</sub>                                                         | - 40                |                        | -                 | dB                   |

| Quiet Battery Noise Rejection<br>(1.0 kHz @ 1.0 V <sub>RMS</sub> )                                                                                                                                                                                         | 3      | V <sub>TX</sub> /V <sub>qb</sub>                                                         | _                   | - 6.0                  | _                 | dB                   |

| Sense Current<br>Tip<br>Ring                                                                                                                                                                                                                               | 4      | <sup> </sup> TSO <sup>/ </sup> TSI<br><sup> </sup> RSO <sup>/ </sup> RSI                 | 0.15<br>0.15        | 0.17<br>0.17           | 0.19<br>0.19      | mA/mA                |

| Fault Currents Tip to V <sub>CC</sub> Ring to V <sub>CC</sub> Tip to Ring Tip and Ring to V <sub>CC</sub>                                                                                                                                                  | 1      | I <sub>Tip</sub><br>IRing<br>ILoop<br>ITip and I <sub>Ring</sub>                         | _<br>_<br>          | 0<br>2.5<br>120<br>2.5 | _<br>_<br>_<br>   | mA                   |

| Analog Ground Current                                                                                                                                                                                                                                      | 1      | l <sub>VAG</sub>                                                                         | _                   | 0.1                    | 2.0               | μΑ                   |

| Powerdown Logic Levels                                                                                                                                                                                                                                     |        | IPDI<br>VIH<br>VIL                                                                       | -<br>-1.2<br>-      | -1.0<br>-<br>-         | -10<br>-<br>-4.0  | μΑ<br>Vdc<br>Vdc     |

| Hook Status Output Current $ \begin{array}{ll} (R_L < 2.5 \text{ k}\Omega, \text{VHSO} = +0.4 \text{ Vdc}) \\ \text{VHSO} = -0.4 \text{ Vdc}) \\ (R_L > 10 \text{ k}\Omega, \text{VHSO} = +12 \text{ Vdc}) \\ \text{VHSO} = -12 \text{ Vdc}) \end{array} $ | 1      | lHSO                                                                                     | + 1.0<br>- 0.4<br>- | + 3.0<br>- 1.5<br>0    | <br>+ 50<br>- 2.0 | mA<br>mA<br>μA<br>μA |

FIGURE 1 - AC TEST CIRCUIT

FIGURE 2 — LONGITUDINAL BALANCE TEST CIRCUIT

FIGURE 3 — SUPPLY NOISE REJECTION TEST CIRCUIT

FIGURE 4 -- TSO AND RSO SUPERVISORY OUTPUT TEST CIRCUIT

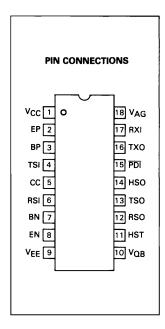

# PIN DESCRIPTIONS

| Pin  | Name            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>CC</sub> | The positive supply voltage. This point is ground in typical applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2, 8 | EP & EN         | Loop current sensing inputs. These are connected to the emitters of the PNP and NPN Darlington transistors. They are tied through 10 $\Omega$ resistors to V <sub>CC</sub> and V <sub>EE</sub> , respectively. The maximum continuous current through these inputs is 240 mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3, 7 | BP & BN         | Base drive outputs. These pins drive the bases of the PNP and NPN transistors and are able to sink or source, respectively, up to 5.0 mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4, 6 | TSI & RSI       | Tip and Ring voltage Sensing Inputs. They are low impedance inputs (approximately 600 $\Omega$ each i.e., 400 $\Omega$ + 3 diodes) that translate the voltages on Tip and Ring to a current through resistors R <sub>T</sub> and R <sub>R</sub> . TSI is referenced to V <sub>CC</sub> and RSI is referenced to V <sub>QB</sub> . These pins have 6.0 V zener diodes (to their respective reference) for protection against overvoltage line surges.                                                                                                                                                                                                                                                                                                     |

| 5    | сс              | Compensation Capacitor pin. This pin is used to stabilize the longitudinal or common mode circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9    | VEE             | Negative supply voltage. This pin ties to the chip substrate. Its operating voltage range is -20 V to -56 V. It can withstand -60 V without damage and can sustain a voltage surge to -75 V for less than 4.0 ms without significant degradation of performance. Most of the loop current and bias currents flow through this pin.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10   | VQB             | Quiet Battery Voltage reference. This is the voltage reference for the RSI pin. Its voltage must not go more negative than VEE. The current through this pin, while powered up, is proportional to the loop current, allowing it to be used for loop current limiting. The voltage on this pin, less 4 volts, is the "effective battery feed voltage for the 2-wire lines even though most of the power comes from the VEE supply.                                                                                                                                                                                                                                                                                                                       |

| 11   | нѕт             | Hook Status Threshold programming resistor input. R <sub>H</sub> determines the value of loop resistance at which on-hook and off-hook status is switched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12   | RSO             | Ring Sense current Output. This output reflects the voltage status of the Ring terminal for voltages more positive than VQB. The current is sourced from this output, it is one-sixth IRSI, its voltage range is 0 to $-20 \text{ V}$ and its saturation voltage is approximately $-2.0 \text{ V}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13   | тѕо             | Tip Sense current Output. This output reflects the voltage status of the Tip terminal for voltages more negative than V <sub>CC</sub> . The current is sourced from this output, it is one-sixth I <sub>TSI</sub> , its voltage range is 0 V to -20 V and its saturation voltage is approximately -2.0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14   | HSO/HSO         | Hook Status Output. This is a digital output that reflects the condition of the loop resistance. If loop resistance is less than a predetermined value established by $R_{H}$ , usually $R_{L} < 2.5~k\Omega$ , the HSO pin will be active, i.e., with positive voltage logic (a resistor tied from a $+5.0~V$ or $+12~V$ supply to HSO), this pin will sink current to $V_{CC}$ (VHSO $\cong 0~V$ ); with negative voltage logic (a resistor tied from a $-12~V$ supply to HSO), this pin will source current from $V_{CC}$ (VHSO $\cong 0~V$ ). If loop resistance is greater than a predetermined value again established by the same resistor $R_{H}$ , usually $R_{L} > 10~k\Omega$ , the HSO pin is inactive, i.e., VHSO $= logic$ supply voltage. |

| 15   | PDI             | Powerdown Input pin. This pin is used to deny service to the subscriber. A logic level "O" ( $V_{\rm IL} < -4.0$ V) powers down the MC3419-1 except for HSO, TSO and RSO. The voltage range of this high impedance input pin is $\pm15$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16   | тхо             | Transmit current Output. This output sinks current to $V_{OB}$ and is proportional to $I_{TSI} + I_{RSI}$ by a ratio of K1 where: K1 = 0.51. Its saturation voltage is $V_{OB} + 2.5$ V typ. (+3.5 V over the temperature range). This pin is only active during the off-hook power-up condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17   | RXI             | Receive Input. This input sums ac currents from TXO and the receive voltage input ( $V_{RX}$ ) and sources all the dc current to TXO. It has a low input impedance (15 $\Omega$ ) typically biased 4.5 V below the $V_{AG}$ pin voltage during off-hook power-up conditions. During powerdown conditions, the voltages on RXI and TXO can drift up to $V_{AG}$ .                                                                                                                                                                                                                                                                                                                                                                                         |

| 18   | VAG             | Analog Ground Voltage reference input. The input impedance of this pin is much greater than 1.0 M $\Omega$ . It should be ac coupled to system ground and could be direct coupled if system ground is between 0 V and $-12$ V. AC coupling requires 300 k $\Omega$ to VCC and 0.1 $\mu$ F to system ground. If VCC and system ground are common, tie VAG directly to VCC. If dc loop currents are allowed to go higher than 60 mA, VAG should be biased from $-2.5$ V to $-12$ V to avoid problems at high ambient temperatures.                                                                                                                                                                                                                         |

#### **FUNCTIONAL DESCRIPTION**

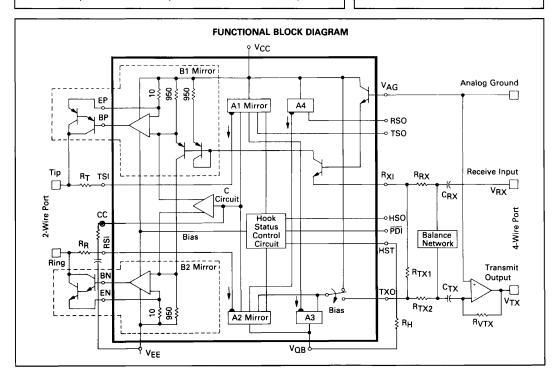

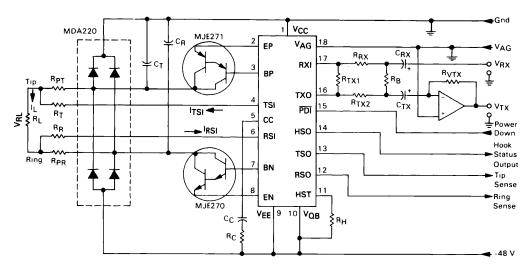

Referring to the functional block diagram on page 1, line sensing resistors ( $R_R$  and  $R_T$ ) at the TSI and RSI pins convert voltages at the Tip and Ring terminals into currents which are fed into current mirrors\* A1 and A2. An output of A1 is mirrored by A3 and summed together with an output of A2 at the TXO terminal. Thus, a differential to single-ended conversion is performed from the ac line signals to the TXO output.

All the dc current at the TXO output is fed back through the RXI terminals to the B1 mirror input. The inputs to B1 and B2 are made equal by mirroring the B1 input current to the B2 input through a unity gain output of the B1 mirror. Both B1 and B2 mirrors have high gain outputs (x95) which drive the subscriber lines with balanced currents that are equal in amplitude and 180° out of phase. The feedback from the TXO output, through the B-Circuit mirrors, to the subscriber line produces a dc feed resistance significantly less, but proportional to the loop sensing resistors.

In most line-interface systems, the ac termination impedance is desired to be greater than the dc feed impedance. A differential ac generator on the subscriber loop would be terminated by the dc feed impedance if the total ac current at the TXO output were returned to the B1 input along with the dc current. Instead, the MC3419-1 system diverts part of the ac current from the B-Circuit mirrors. This decreases the ac feedback current, causing the ac termination impedance at the line interface to be greater than the dc feed impedance.

The ac current that is diverted from the B1 mirror input is coupled to a current-to-voltage converter circuit that has a low input impedance. This circuit consists of an op amp (external to the MC3419-1) and a feedback resistor which produces the transmit output voltage (VTX) at the 4-wire interface. Transmission gain is programmed by the op amp feedback resistor (RVTX).

Reception gain is realized by converting the ac coupled receive input voltage  $(V_{RX})$  to a current through an external resistor  $(R_{RX})$  at the low impedance RXI terminal. This current is summed at RXI with the dc and ac feedback current from the A-Circuit mirrors and drives the B1 mirror input. The B-Circuit mirror outputs drive the 2-wire port with balanced ac current proportional to the receive input voltage. Reception gain is programmed by the  $R_{RX}$  resistor.

Since receive input signals are transmitted through the MC3419-1 to the 2-wire port, and the 2-wire port signals are returned to the 4-wire transmit output, a means of cancellation must be provided to maintain 4-wire signal separation (transhybrid rejection). Cancellation is complicated because the gain from the receive port to the transmit port depends on the impedance

of the subscriber loop. A passive "balance network" is used to achieve transhybrid rejection by cancelling, at the low impedance input to the transmit op amp, the current reflected by the loop impedance to the 4-wire transmit output. For a resistive loop impedance, a single resistor provides the cancellation. For reactive loops, the balance network should be reactive.

Longitudinal (common-mode) currents that may be present on the subscriber lines are suppressed in the MC3419-1 by two methods. The first is inherent in the mirror configuration. Positive-going longitudinal currents into Tip and Ring create common-mode voltages that cause a decreasing current through the Tip Sensing resistor and an increasing current through the Ring Sensing resistor. When these equal and opposite signal currents are reflected through the A-Circuit mirrors and summed together at TXO, the total current at TXO remains unchanged. Therefore, the ac currents due to the common-mode signal are cancelled before reaching the transmit output.

The second longitudinal suppression method is more dominant, since it limits the amplitude of common-mode voltages that appear at the Tip and Ring terminals.

A common-mode suppression circuit detects common-mode inputs and drives the loop with balanced currents to reduce the input amplitude. Subtracting currents from outputs of the A1 and A2 mirrors produces a signal current at the CC terminal in response to the common-mode voltage at Tip and Ring. A transconductance amplifier (C-Circuit) generates a current proportional to the CC terminal voltage which is summed with the current from the RXI terminal at the inputs of current mirrors B1 and B2. The weighting and polarity of the summing networks produce common-mode B1 and B2 mirror output currents at the 2-wire port. The common-mode input impedance is inversely proportional to the gain of the longitudinal suppression circuit. Rc and Cc compensate the common-mode feedback loop. At 60 Hz with typical component values, the 2-wire common-mode impedance is less than 5  $\Omega$ .

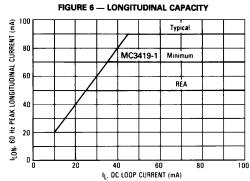

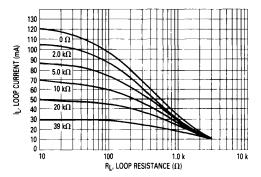

The longitudinal suppression circuit output currents are generated by modulating dc current fed to the loop by the B1 and B2 current mirrors. This configuration avoids the increased power dissipation attributed to current mode loop drive because dc and longitudinal currents are not cumulatively sourced to the loop. However, driving common-mode currents through the B-circuit current mirrors in this manner limits the longitudina suppression capability. The suppression circuit is unable to reverse 2-wire current polarities to maintain a low-impedance termination when longitudinal currents exceed the dc loop current. At low dc loop currents, the common-mode signal capability, known as longitudinal capacity, is limited by the loop current (Figure 6). At high-loop currents, longitudinal capacity is limited by the maximum voltage swing of the CC terminal and is therefore independent of dc loop current.

<sup>\*</sup>A current mirror is a circuit which behaves as a current controlled current source. It has a single low-impedance input terminal with respect to a reference point and one or more high impedance outputs.

FIGURE 7 - BASIC SLIC CIRCUIT

The hook status control circuit supplies the bias currents to activate the B-Circuit op amps and other sections of the MC3419-1. To activate the bias currents, the control circuit compares the current through the sense resistors, RR and RT, and the load resistance RL with the current through the hook status threshold programming resistor, RH, by using outputs from both A1 and A2 mirrors. The A1 mirror output sources current to the RH resistor. (This reduces all internal currents to near zero during the on-hook state in order to eliminate unnecessary power consumption.) If this current is large enough the voltage on the HST pin will trip an internal comparator, then another circuit compares the current from the A1 output with that of an A2 output. These currents must match within ±15%. If so, HSO will be activated and the bias circuits will turn on provided the voltage on PDI is greater than -1.2 V. The HSO pin can have either a pull-up resistor or a pull-down resistor and when activated it will switch to V<sub>CC</sub> (0 volts).

Once the MC3419-1 is powered up, a circuit with a gain of 20 feeds current to the  $R_{\rm H}$  resistor in order to keep the bias circuitry active. (The sense resistors are paralleled with the Darlington transistors which reduces

the sense input currents.) Should the sense input currents drop below one-twentieth of the required powerup current, the bias currents will be removed, forcing a power-down condition.

Current mode analog signal processing is critically dependent on voltage to current conversion at the 2-wire and 4-wire inputs. Precise, low-noise voltage sensing through resistors R<sub>T</sub>, R<sub>R</sub> and R<sub>RX</sub> requires quiet, low impedance terminations at terminals TSI, RSI and RXI respectively. For 2-wire signals, terminal V<sub>QB</sub> isolates the loop-sensing resistors and current mirrors from noise at the high-current V<sub>EE</sub> terminal. External filtering from V<sub>CC</sub> to V<sub>QB</sub> ("quiet battery" terminal) ensures loop voltages are sensed without interference from system supply noise. V<sub>EE</sub> noise rejection at audio frequencies is typically 60 dB or greater.

Receive input terminal RXI is referenced to the V<sub>AG</sub> terminal which references the 4-wire input to the "analog ground" of the 4-wire signal source, thus isolating the input from power ground voltage transients. This isolation offers 70 dB of noise rejection at audio frequencies.

#### SYSTEM EQUATIONS

K1 — The current gain from  $I_{TSI} + I_{RSI}$  to TXO only during an off-hook power-up condition. K1 = 0.51  $\pm$  1%.

K2 — The current gain from RXI to the collectors of the off-chip Darlington transistors only during an off-hook power-up condition. K2 =  $95 \pm 1\%$ .

For simplicity, the following equations do not use K1 or K2. Instead the actual numerical value is used, for instance  $(1 + [2]K1K2) = 1 + 1.02 \times 95 = 97.9$  is approximately 98.

R<sub>L</sub> — Loop resistance. This is a load resistance from Tip to Ring and can be either ac or dc depending on context.

#### **LOOP CURRENT REGULATIONS**

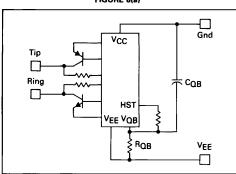

FIGURE 8(a)

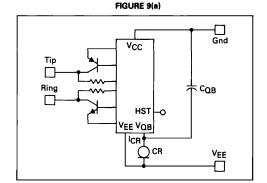

FIGURE 8(b)

FIGURE 9(b)

#### SYSTEM EQUATIONS (continued)

Z<sub>L</sub> — Loop impedance. This is used only to connote a complex impedance loading on Tip and Ring.

I<sub>1</sub> — Loop current. The dc current flow through R<sub>L</sub>.

$R_F$  — Dc feed resistance. The synthesized resistance from which battery (V<sub>CC</sub> and V<sub>EE</sub>) current is fed to R<sub>L</sub>. The battery feed resistance is balanced differential feed. See Figure 7. (This assumes V<sub>QB</sub> = V<sub>EE</sub>.) The first order equation is:

$$R_{F} = \frac{R_{R} + R_{T} + 1200 \,\Omega}{98} \tag{1}$$

Because of the diode voltage drops on TSI and RSI, the actual dc feed resistance is higher. The second order equation is:

$$R_F = \frac{|V_{QB}|(98 \ R_L + R_R + R_T + 1200 \ \Omega)}{98 \ (|(V_{QB}| - 4.0 \ V)} - R_L \qquad (2)$$

ignoring the effects of RL

$$R_F = \frac{|V_{QB}|(R_R + R_T + 1200 \Omega)}{98 (|V_{QB}| - 4.0 V)}$$

(3)

So:

$$R_R = R_T = \frac{49R_F (|V_{QB}| - 4.0 \text{ V})}{|V_{QB}|} - 600$$

(4)

The minimum value for RR and RT is 5.0 k $\Omega$ .

The first order value of RF can not be greater than the desired value of the termination impedance (usually 600  $\Omega$  or 900  $\Omega$ ). To achieve dc feed resistances that are greater, a resistor can be placed between VQB and VEE along with a filter capacitor CQB which restores the desired termination impedance and filters power supply noise. A diode should also be placed between VQB and VEE to prevent damage in case a catastrophic power supply failure occurs.

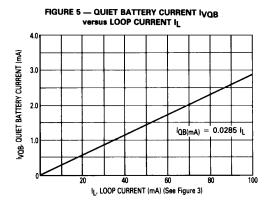

$I_{VQB}$  — This is the current that is sourced from the  $V_{QB}$  pin and is proportional to the currents into and out of RSI and TSI. When the SLIC is in the off-hook power-up mode,  $I_{VQB}$  is also proportional to  $I_{L}$ .

$$i_{VQB} = 2.15 i_{RSI} + 0.7 i_{TSI}$$

(5)

$$I_{VQB} = 0.029 I_{E}$$

(6)

$R_{FQ}$  — Dc feed resistance. The synthesized resistance from which battery current is fed to  $R_L$ , see Figure 8. (This assumes  $V_{QB}$  is tied to  $V_{EE}$  through a resistor  $R_{QB}$ .)  $R_{QB}$  synthesizes additional dc feed resistance to the  $R_F$  value previously stated.

When using RQB, the dc feed is effectively balance fed from VCC and VQB instead of VEE. The sense resistors (RR and RT) should be selected to make RF (first order) less than the termination impedance.

$$R_{FQ} = \frac{|V_{EE}|(98R_L + R_R + R_T + 1200 + 2.85R_{QB})}{98(|V_{EE}| - 4.0 \text{ V})} - R_L$$

(7)

Ignoring RI, this simplifies to:

$$R_{FQ} = \frac{|V_{EE}|(R_R + R_T + 1200 + 2.85R_{QB})}{98(|V_{EE}| - 4.0 \text{ V})}$$

(8)

Therefore:

$$R_{QB} = \frac{98R_{FQ}(|V_{EE}| - 4.0 \text{ V}) - |V_{EE}|(R_R + R_T + 1200 \Omega)}{2.85|V_{EE}|}$$

(9)

COB — Power supply noise filter capacitor.

$$C_{QB} = \frac{2.85 R_{QB} + R_{R} + R_{T} + 1200 \Omega}{2\pi f R_{QB} (R_{R} + R_{T} + 1200 \Omega)}$$

(10)

Figure 9B shows RQB replaced with a current regulating device such as Motorola's 1N5283 family.

$I_{CRQB}$  — The current that is sourced to a current regulating device from the  $V_{QB}$  pin. When this current reaches the regulated value, the voltage differential between  $V_{EE}$  and  $V_{QB}$  increases causing the effective battery voltage to decrease which limits  $I_L$  to a maximum value as determined below:

$$I_{L} = 34.5 I_{CRQB} \tag{11}$$

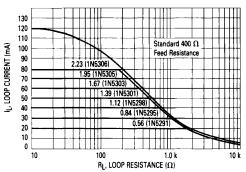

The graph, Figure 9B, shows loop current versus loop resistance using several values of I<sub>CRQB</sub>. The closest current regulating diode part number to that value is also shown. A typical value for C<sub>QB</sub> in this case is 10  $\mu\text{F}$ , 60 Vdc.

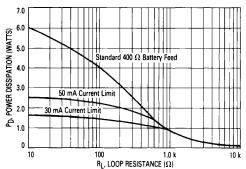

Figure 10 shows how power can be conserved on the shorter loop lengths by utilizing current limiting techniques.

Overvoltage protection on the 2-wire port is achieved with the MDA220 diode bridge and the protection resistors RpR and RpT. Whenever the voltage on the 2-wire port exceeds the power supply rails (V<sub>CC</sub> and V<sub>EE</sub>), the MDA220 diodes will forward bias and "clamp" to the rail voltage. The current is limited by the protec-

FIGURE 10 — TOTAL SLIC POWER DISSIPATION Versus LOOP RESISTANCE

tion resistors. These resistors should be as large in value as possible. However, if they are too large, they will interfere with the performance of the SLIC under worst case conditions.

$$R_{PT} < R_{T}/196 - 15$$

(12)

Using the voltage of  $V_{QB}$  when  $I_L$  is at its minimum off-hook value (Typ. 20 mA):

$$R_{PR} < R_{R}/196 + 25|V_{EE} - V_{QB}| - 15$$

(13)

The tolerance of these resistors is not critical due to placement inside a closed loop. Positive temperature co-efficient resistors (PTC) may be considered here. Consult resistor manufacturers for component selections that will meet the surge current and peak voltage requirements.

Because the MC3419-1 is a broadband device it requires compensation components to keep its circuits stable.

C<sub>R</sub> & C<sub>T</sub> — Compensates the longitudinal gain of the A and the B circuit mirrors. Their values range from 2000 pF to 5000 pF.

R<sub>C</sub> & C<sub>C</sub> — Compensates the longitudinal "C" circuitry. Their values can be ratioed according to:

$$R_{C} \times C_{C} = R_{T} \times C_{T}. \tag{14}$$

Two off-chip power Darlington transistors are used with the MC3419-1. These transistors reduce any temperature gradiant problems with the precision matched devices on-chip and they alleviate thermal stress conditions that could occur for every on-hook and off-hook transition. The power dissipation in these devices is:

$$P_{QT} = I_L^2(R_T/98 - R_{PT} - 4) + (2.0 \text{ V})I_L$$

(15)

$$P_{QR} = I_L [|V_{EE}| - 2 - I_L(R_T/98 + R_L + R_{PR} + 16)]$$

(16) where  $I_L = |V_{EE}|/R_{FQ}$  or  $I_L(max)$  in current limited designs

#### SYSTEM EQUATIONS (continued)

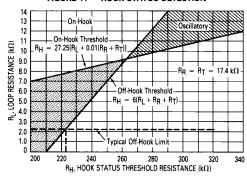

$R_H$  — The resistor that determines the hook status threshold values of  $R_L$ .  $R_H$  is selected from a graph of the following two equations:

Off-hook threshold

$$R_{H} = 6(R_{L} + R_{R} + R_{T})$$

(17)

On-hook threshold

$$R_H = 27.25 [R_L + 0.01(R_R + R_T)]$$

(18)

#### FIGURE 11 — HOOK STATUS DETECTION

Figure 11 shows such a graph using 17.4 k $\Omega$  as the values for R<sub>R</sub> and R<sub>T</sub>. Note the oscillatory condition to the right of the crossing point. Selection of R<sub>H</sub> in this region is usually not a problem since the majority of telephone lines do not fall into this resistance range. R<sub>H</sub> always ties to V<sub>QB</sub> and HST and will give reliable hook status information regardless of power supply voltages and PDI.

$R_{O}$  — Termination impedance of the 2-wire port. This impedance is greater than the dc feed resistance  $R_{F}$  because of a current splitting network in the feedback loop,  $R_{TX1}$  and  $R_{TX2}$ .

K3 — A constant, formed by  $R_{TX1}$  and  $R_{TX2}$ , between 0 and 1, which determines the ratio of the first order value of  $R_F$  to  $R_O$ .

$$R_{O} = \frac{R_{R} + R_{T} + 1200 \Omega}{1 + 97K3}$$

(19)

So:

$$K3 = \frac{R_{R} + R_{T} + 1200 \Omega - R_{O}}{97R_{O}}$$

(20)

and

$$K3 = \frac{R_{TX2} + Z_{in}}{R_{TX1} + R_{TX2} + Z_{in}}$$

(21)

Z<sub>in</sub> — The input impedance of the current to voltage converter op amp. This impedance is usually negligible, it can be used to sway the selection of a 1% component value.

$$Z_{\text{in}} = \frac{(R_{\text{R}} + R_{\text{T}} + 1200 \,\Omega) \,G_{\text{TX}}}{1020 \,(1 - K3)} = \frac{R_{\text{VTX}}}{1000} \tag{22}$$

$R_{TX1}$  — Feeds most of the TXO dc current to the RXI pin. To keep TXO from saturation the maximum value of  $R_{TX1}$  is as follows:

$$R_{TX1} < \frac{(R_R + R_T + 1200 \,\Omega) \, (|V_{OB}|min - |V_{AG}|max - 6.5 \,V)}{|V_{OB}|min - 5.4 \,V} \end{(23)}$$

Where:

$$|V_{QB}|min = \frac{(R_R + R_T + 1200 \Omega) (|V_{EE}|min - 4)}{(R_R + R_T + 1200 \Omega + 2.8 R_{QB})}$$

(24)

or If a current regulator diode is used:

$$R_{TX1} < \frac{0.01 \; I_L(max) \; (R_R + R_T + 600 \; \Omega) - |V_{AG}|max - 3.9 \; V}{0.01 \; I_L(max)} \tag{25}$$

It is beneficial to make  $R_{TX1}$  as large as possible. Typical values range from 15 k to 24  $k\Omega.$

$$R_{TX2} = \frac{K3 R_{TX1}}{1 - K3} - Z_{in}$$

(26)

$$C_{TX} = \frac{R_R + R_T + 1200 \Omega}{7R_{TX2}}$$

The result is in  $\mu$ F. (27)

$G_{TX}$  — The voltage gain from the 2-wire port to  $V_{TX}$  which is adjustable by  $R_{VTX}$ .

$$G_{TX} = \frac{1.02 (1 - K3) R_{VTX}}{R_R + R_T + 1200 \Omega}$$

(28)

$$R_{VTX} = \frac{G_{TX}(R_R + R_T + 1200 \Omega)}{1.02 (1 - K3)}$$

(29)

$G_{RX}$  — The voltage gain from the  $V_{RX}$  input to the 2-wire port which is adjustable by  $R_{RX}$ .

$$G_{RX} = \frac{-95 R_L (R_R + R_T + 1200 \Omega)}{R_{RX} [(R_R + R_T + 1200 \Omega) + R_L(1 + 97K3)]}$$

(30)

$$G_{RX} = \frac{-95 R_L R_O}{R_{RX}(R_L + R_O)}$$

(31)

$$R_{RX} = \frac{95 R_L R_O}{G_{RX}(R_L + R_O)}$$

(32)

$$C_{RX} > \frac{R_{RX} + R_B}{2\pi f R_{RX} R_B}$$

(33)

Where f is the minimum passband frequency, usually

Transhybrid Rejection — The voltage gain from  $V_{RX}$  to  $V_{TX}$ . It is expressed in dB, the number should be negative and the larger the value the better. Transhybrid rejection is achieved by summing a current from the  $V_{RX}$  input (RB) with the TXO current that flows to the current to voltage converter. RB balances a resistive load, RI.

$$R_{B} = \frac{R_{RX}(1 + 97K3) (R_{O} + R_{L})}{97R_{L} (1 - K3)}$$

(34)

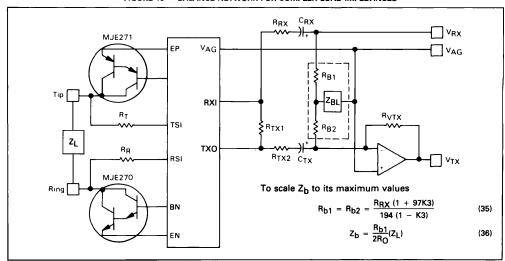

CRX R<sub>RX</sub> **MJE271** ΕP VAG ξR<sub>b1</sub> вР Tip RXI  $\dot{c}_{\text{B}}$ **RVTX** TSI ₹R<sub>TX1</sub> R<sub>b2</sub> TXO RR R<sub>TX2</sub> RSI CTXMJE270

FIGURE 12 — BALANCE NETWORK FOR CAPACITIVE LINES

FIGURE 13 — BALANCE NETWORK FOR COMPLEX LOAD IMPEDANCES

When the 2-wire port has a parallel R and C load, then (see Figure 12):

$$R_{b1} = \frac{R_{RX}(R_{R} + R_{T} + 1200 \Omega)}{97R_{L} (1 - K3)}$$

(37)

$$R_{b2} = \frac{R_{RX}(R_R + R_T + 1200 \Omega)}{97R_O(1 - K3)}$$

(38)

$$C_b = \frac{R_L C_L}{R_{b,a}} \tag{39}$$

ΒN

ΕN

When it is desirable to balance complex load imped-

ances using component values that are equal to the load values (see Figure 13) then:

$$R_{b1} = \frac{R_{RX}(1 + 97K3)}{194(1 - K3)} + \sqrt{\left[\frac{R_{RX}(1 + 97K3)}{194(1 - K3)}\right]^2 - \frac{R_{Q}R_{RX}(1 + 97K3)}{97(1 - K3)}}$$

(40)

$$R_{b2} = \frac{R_{RX}(1 + 97K3)}{97(1 - K3)} - R_{b1}$$

(41)

$$Z_b = Z_L$$

(42)

R<sub>b1</sub> and R<sub>b2</sub> values are interchangeable.

#### SYSTEM EQUATIONS (continued)

The Tip and Ring Sense Output currents are proportional to the currents out of and into TSI and RSI, respectively.

$$I_{TSO} = \frac{I_{TSI}}{S}$$

(4)

$$I_{RSO} = \frac{I_{RSI}}{s} \tag{44}$$

$$I_{TSO} = \frac{|V_{Tip} - V_{CC}| - 2.0 \text{ V}}{6 (R_T + 600 \Omega)} \text{ for } V_{Tip} < V_{CC}$$

(45)

$$I_{RSO} = \frac{|V_{Ring} - V_{QB}| - 2.0 \text{ V}}{6(R_R + 600 \Omega)} \text{ for } V_{Ring} > V_{QB}$$

(46)

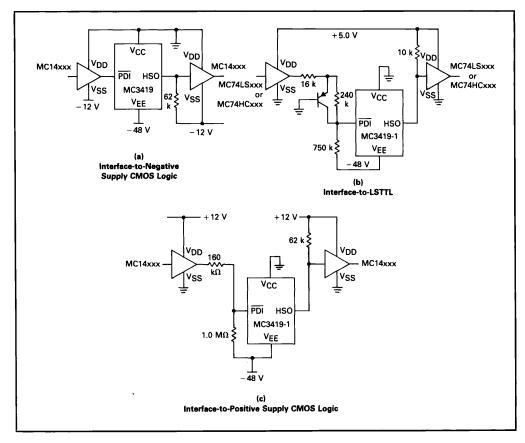

Digital interfacing to the MC3419-1  $\overline{\text{PDI}}$  pin and the HSO pin is shown in Figures 14a, 14b and 14c. If the  $\overline{\text{PDI}}$  pin is not used it should be terminated to  $V_{CC}$  and if HSO is not used, it can be left open.

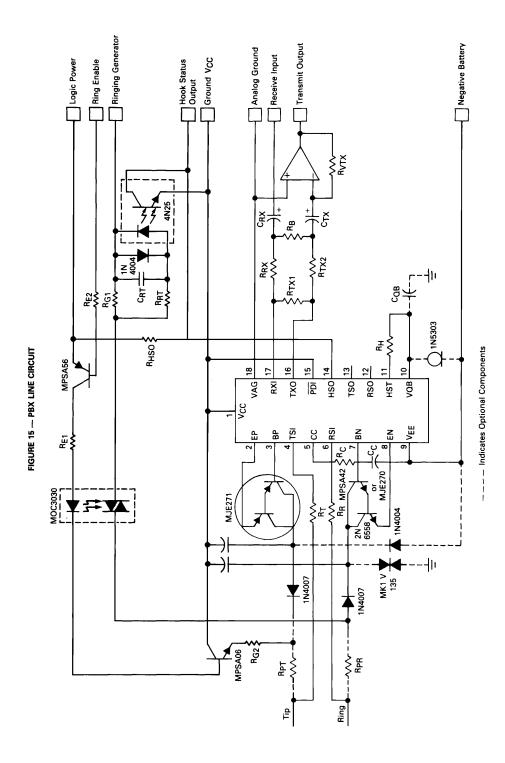

Figure 15 is an application circuit showing solid state ringing insertion using an MOC3030 zero-crossing detector optocoupled triac to replace the conventional electromechanical relay. This device inserts the ringing signal on a zero voltage crossing which eliminates noise in adjacent cable pairs and removes the signal on a zero current crossing which eliminates inductive voltage spikes that commonly destroy relay contacts. The ringing generator provides a continuous 40 V to 120 V RMS signal from 15 to 66 Hz superimposed upon –48 Vdc. Ringing cadencing is inserted with the Ring Enable Input. The 2N6558 and MPSA42 replace the MJE270 for systems that use ringing generator voltages greater than 70 V<sub>RMS</sub>. The MDA220 diode bridge is replaced with a series 1N4007 on the Tip lead and a shunting 1N4004 to V<sub>EE</sub> and to allow ringing voltage

FIGURE 14 -- INTERFACE-TO-DIGITAL LOGIC

# SYSTEM EQUATIONS (continued)

on the Ring lead to exceed the power supply voltages, a 1N4007 and an MK1V-135 (Sidac) are used for protection. The forward voltage drop across the 1N4007, during normal operation, will not affect the parametric characteristics of the MC3419-1 since it is "inside" a feedback circuit. If the MJE270 is used, the MK1V-135 should be replaced with a lower voltage Sidac or MO+sorb transient suppressor.

An optocoupled transistor circuit is used for ring trip detection on long lines. It samples only the ac and dc ringing signal current and uses a simple one pole filter to eliminate the low level ac signal. Under worst case conditions this circuit will ring trip in 1½ to 4 cycles. In

systems serving only short loops (<700  $\Omega)$ , if R<sub>G1</sub> and R<sub>G2</sub> are 620  $\Omega$  or greater, the optotransistor circuit is not needed, the Hook Status Output will perform ring trip on a Zero Crossing. The Ring Enable input and the Hook Status Output interface with standard CMOS and TTL logic.

The op amp in this circuit is an integral part of the following codecs, filters or combos:

MC3417/8 — MC145414 MC14404/6/7 — MC14413/4 MC14401/2/3/5

#### LONG LINES OFF-PREMISE LINES

| Specifications            |                    |                       |                       | Off-Hook          | <2500 Ω            | V <sub>Logic</sub> +5.0 V          |

|---------------------------|--------------------|-----------------------|-----------------------|-------------------|--------------------|------------------------------------|

| R <sub>F</sub><br>IL(max) |                    |                       | - 600 Ω<br>- 0 dB     | On-Hook           | >10 kΩ             | VEE - 42 to -56                    |

| _                         |                    |                       | 200-3400 Hz           | Protection        | 1000 V             | V <sub>Ringing</sub> (40 V to 120  |

| RL(max)                   | — 1900 Ω           | T <sub>χ</sub> Gain — | - 0 dB<br>200–3400 Hz | Ringer Equivalent | 5                  | V <sub>RMS</sub> )+V <sub>EE</sub> |

| Parts List                |                    |                       |                       |                   |                    |                                    |

| MPSA56                    | R <sub>R</sub> —   | 9.09 k                | 1% Matched            | MOC3030           | R <sub>TX1</sub> — | 12.1 k 1%                          |

| 2N3905                    | R <sub>T</sub> —   | 9.09 k                | 1% if desired         | 4N25              | R <sub>TS2</sub> — | 5.76 k 1%                          |

| 2N6558                    | RPT -              | 47 Ω !                | 5%                    |                   | R <sub>RX</sub> —  | 28.7 k 1%                          |

| MPSA42                    | R <sub>PR</sub> —  | 75 Ω                  | 5%                    |                   | R <sub>B</sub> —   | 28.0 k 1%                          |

| MJE271                    | RG1 —              | 620 Ω                 | 5%                    |                   | R <sub>VTX</sub> — | 28.6 k 1%                          |

| 1N4007                    | RG2 —              | 100 Ω                 | 5%                    |                   | CT                 | 0.004 μF                           |

| MK1V135                   | R <sub>E1</sub> —  | 91 Ω                  | 5%                    |                   | C <sub>R</sub> —   | 0.004 μF                           |

| 1N4007                    | RE2 —              | 3.0 k                 | 5%                    |                   | c <sub>c</sub> –   | 0.001 μF                           |

| 1N4007                    | R <sub>RT</sub> —  | 20 k                  | 5%                    |                   | C <sub>RX</sub> —  | 1.0 μF/20 V                        |

| 1N5303                    | R <sub>C</sub> —   | 24 k                  | 5%                    |                   | c <sub>tx</sub> —  | 2.0 μF/40 V                        |

| 1N4004                    | RH —               | 127 k 1–3             | 3%                    |                   | C <sub>RT</sub> —  | 20 μF/5.0 V                        |

| MC3419-1                  | R <sub>HSO</sub> — | 10 k                  | 5%                    |                   | COB —              | 10 μF/60 V                         |

#### **SHORT LINES ON-PREMISE LINES**

# Specifications - 500 Ω Rr - 700 Ω

| Rլ (max)          |   | 700 Ω        |

|-------------------|---|--------------|

| Ring Trip         | _ | <50 ms       |

| Ringer Equivalent | - | 2.5          |

| RO                | - | 600 $\Omega$ |

| Parts List |     |   |        |    |

|------------|-----|---|--------|----|

| MJE271     | RR  | _ | 19.6 k | 1% |

| MJE270     | RT  | _ | 19.6 k | 1% |

| MPSA56     | RG1 | _ | 620 Ω  | 5% |

| 2N3905     | RG2 | _ | 620 Ω  | 5% |

| 1N4007     | RF1 | _ | 91 Ω   | 5% |

| 1N4007     | RE2 | _ | 3.0 k  | 5% |

| R <sub>X</sub> Gain | _ | -5.0 dB                 |

|---------------------|---|-------------------------|

| Tx Gain             |   | 0 dB                    |

| V <sub>Logic</sub>  | _ | +5.0 Volts              |

| VFF                 | _ | -20 to -56 Volts        |

| VRinging            | _ | (40 V to 70 VRMS) + VEE |

| MOC3 | 030 |       |    | RHSO             | _ | 10 k   | 5% |

|------|-----|-------|----|------------------|---|--------|----|

|      |     |       |    | RTX1             | _ | 19.6 k | 1% |

| CT   | _   | 0.004 | μF | R <sub>TX2</sub> | _ | 42.2 k | 1% |

| CR   | _   | 0.004 | μF | R <sub>RX</sub>  |   | 69.8 k | 1% |

| CC   | _   | 0.004 | μF | RB               | _ | 301 k  | 1% |

| CRX  | _   | 0.1   | μF | RVTX             | _ | 127 k  | 1% |

| CTX  | _   | 0.5   | μF | RC               | _ | 56 k   | 5% |