# 32/64-Channel Infinite Sample-and-Hold

# **Preliminary Technical Data**

AD5532/64

#### **FEATURES**

Infinite Hold Capability with No Droop

Single Input, 32/64 Output Channels

Input/Output Transfer Function Nonlinearity of

±0.012% max

Per-Channel Acquisition time of 16 μs max

Input Voltage: 0 to +3V

Output Voltage Span: +10V

e.g. -3V to +7V

-2.5V to +7.5V

#### **APPLICATIONS**

Level Setting Instrumentation Automatic Test Equipment Control Systems Data Acquisition Low Cost I/O

#### GENERAL DESCRIPTION

The AD5532/64 combines a 32/64 channel voltage translation function with an infinite output hold capability. An analog input voltage on the common input pin, V<sub>IN</sub>, is sampled and its digital representation transferred

to a chosen DAC register. The output of this DAC is updated to reflect the new contents of the DAC register. Channel selection is accomplished via the parallel address inputs A0-A5 or via the serial input port.

The device is operated with AVcc =  $+5V\pm5\%$ , DVcc= 2.7V to 5.5V, Vss = -4.75V to -16.5V and V<sub>DD</sub>= 8V to 16.5V and requires a stable +3V reference on REF IN pins as well as an offset voltage on OFFS\_IN. The output voltage range is determined by the headroom of the output amplifier and is restricted to a range from Vss+2.2V to V<sub>DD</sub>-2V. The AD5564 is available in a 119-lead BGA package.

#### PRODUCT HIGHLIGHTS

- 1. No Droop; Infinite Hold Capability

- 2. Typically ±0.006% transfer function nonlinearity between Input and Output.

- 3. 32/64 14-bit DACs in one package, guaranteed monotonic with 9-bit linearity.

- 4. The AD5564 is available in a 119-lead BGA package with a bump pitch of 1.27mm and a body size of 14mm by 22mm.

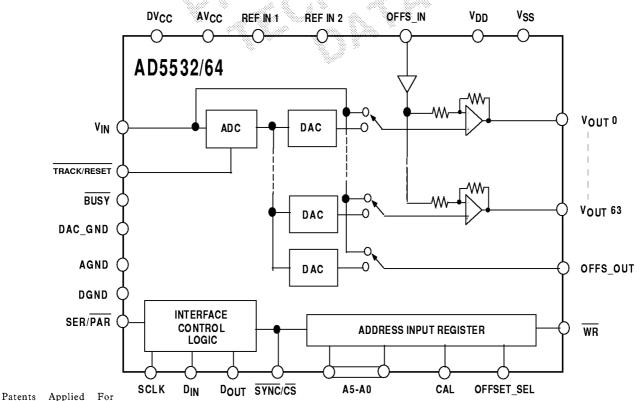

### FUNCTIONAL BLOCK DIAGRAM

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106,USA Tel: 781/329-4700 World Wide Web: www.analog.com Fax: 781/326-8703

REV. PrE

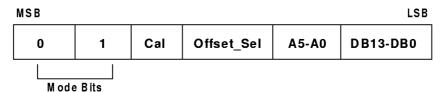

Mode 1 - SHA Mode

$\begin{array}{l} \textbf{AD5532/64-SPECIFICATIONS} \\ \textbf{V}_{\text{DD}} = +8 \text{V to } +16.5 \text{V}, \ \textbf{V}_{\text{SS}} = -4.75 \text{V to } -16.5 \text{V}; \ \textbf{AV}_{\text{CC}} = +4.75 \text{V to } +5.25 \text{V}; \ \textbf{DV}_{\text{CC}} \\ = +2.7 \text{V to } +5.25 \text{V}; \ \textbf{AGND} = D \text{GC}_{\text{GND}} = D \text{AC}_{\text{GND}} = D \text{V}; \ \textbf{Output Range from Vss} +2.2 \text{V to V}_{\text{DD}} -2 \text{V}. \ \textbf{All specifications T}_{\text{MIN}} \ \textbf{to T}_{\text{MAX}} \ \textbf{unless otherwise noted}. \end{array}$

| Parameter <sup>1</sup>                           | B Version <sup>2</sup>       | Units                | Conditions/Comments                                                                                 |

|--------------------------------------------------|------------------------------|----------------------|-----------------------------------------------------------------------------------------------------|

| ANALOG CHANNEL                                   |                              |                      |                                                                                                     |

| V <sub>IN</sub> to V <sub>OUT</sub> Nonlinearity | ± 0.012                      | % max                | Typically ±0.006% (after gain and offset                                                            |

|                                                  |                              |                      | adjustment)                                                                                         |

| Offset Error                                     | ± 60                         | mV max               | See Figure 1 (page 8)                                                                               |

| Gain Error                                       | ± 100                        | mV max               | See Figure 1 (page 8)                                                                               |

| Channel-to-Channel Matching                      | TBD                          | % typ                |                                                                                                     |

| ANALOG INPUT (V <sub>IN</sub> )                  |                              |                      |                                                                                                     |

| Input Voltage Range                              | 0 to +3                      | V                    | Nominal Input Range                                                                                 |

| Input Current                                    | 100                          | nA max               | V <sub>IN</sub> being acquired on one channel                                                       |

|                                                  | 6.4                          | μA max               | V <sub>IN</sub> being acquired on all 64 channels                                                   |

| Input Capacitance                                | 50                           | pF typ               | simultaneously - Cal Mode                                                                           |

|                                                  | J 0                          | pr typ               |                                                                                                     |

| ANALOG INPUT (OFFS_IN)                           | 100                          |                      |                                                                                                     |

| Input Current                                    | 100                          | nA max               |                                                                                                     |

| REFERENCE INPUTS                                 |                              |                      |                                                                                                     |

| Nominal Input Voltage                            | +3.0                         | V                    |                                                                                                     |

| Input Voltage Range                              | +2.85/+3.15                  | V min/max            |                                                                                                     |

| Input Current                                    | 50                           | nA max               | **                                                                                                  |

| ANALOG OUTPUTS (V <sub>OUT</sub> 0-63)           |                              |                      |                                                                                                     |

| Output Temp Coeff                                | 10                           | ppm/°C typ           | AD780 as reference for the AD5532/64                                                                |

| Output Impedance                                 | 1                            | kΩ typ               |                                                                                                     |

| Output Range                                     | $V_{SS}$ +2.2 / $V_{DD}$ - 2 |                      | 100μA load on the output                                                                            |

| Maximum Output Current                           | 500                          | μA typ               |                                                                                                     |

| Maximum Capacitive Load                          | 15                           | nF max               |                                                                                                     |

| Output Noise                                     | 250                          | μV rms               | 1 MHz Bandwidth                                                                                     |

| Short-Circuit Current Output PSRR                | 10<br>-70                    | mA typ<br>dB         | V ratiod +5%                                                                                        |

| Output 13KK                                      | -70<br>  -70                 | dB                   | $egin{array}{lll} V_{DD} & 	ext{varied} & \pm 5\%. \\ V_{SS} & 	ext{varied} & \pm 5\%. \end{array}$ |

| DC Crosstalk                                     | 250                          | μV max               | V <sub>SS</sub> varied 2570                                                                         |

|                                                  |                              | <b>F</b>             |                                                                                                     |

| ANALOG OUTPUT (OFFS_OUT)                         | 10                           | /00                  | AD700                                                                                               |

| Output Temp Coeff Output Impedance               | 10                           | ppm/°C typ<br>kΩ typ | AD780 as reference for the AD5532/64                                                                |

| Output Impedance Output Range                    | 0 / +REF IN                  | V min/max            |                                                                                                     |

| Output Noise                                     | 100                          | μV rms               | 1MHz Bandwidth                                                                                      |

| Maximum Output Current                           | 10                           | μA typ               | Source Current                                                                                      |

| Maximum Capacitive Load                          | 100                          | pF typ               |                                                                                                     |

| Short-Circuit Current                            | 10                           | mA typ               | Sink Current                                                                                        |

| Output PSRR                                      | -70                          | dB typ               | AV <sub>CC</sub> varied ±5%                                                                         |

| DIGITAL INPUTS                                   |                              |                      |                                                                                                     |

| Input Current                                    | ±10                          | μA max               |                                                                                                     |

| Input Low Voltage                                | 0.8                          | V max                | $DV_{CC} = 5V\pm 5\%$                                                                               |

| . 3-                                             | 0.4                          | V max                | $DV_{CC} = 3V\pm10\%$                                                                               |

| Input High Voltage                               | 2.0                          | V min                |                                                                                                     |

| Input Hysteresis (SCLK only)                     | 200                          | mV typ               |                                                                                                     |

| Input Capacitance                                | 10                           | pF max               |                                                                                                     |

|                                                  |                              |                      |                                                                                                     |

|                                                  |                              |                      |                                                                                                     |

NOTES:

<sup>&</sup>lt;sup>1</sup>See Terminology

<sup>&</sup>lt;sup>2</sup>B Version: Industrial temperature range -40°C. to +85°C.

<sup>&</sup>lt;sup>3</sup>Guaranteed by design and characterisation, not production tested

$\begin{array}{l} \textbf{AD5532/64-SPECIFICATIONS} \ \ v_{oo} = +8V \ to \ +16.5V, \ v_{ss} = -4.75V \ to \ -16.5V; \ AV_{cc} = +4.75V \ to \ +5.25V; \ DV_{cc} \\ = +2.7V \ to \ +5.25V; \ AGND = DGND = DAC\_GND = \ 0V; \ Output \ Range \ from \\ \end{array}$ Vss+2.2V to  $V_{DD}$  -2V. All specifications  $T_{MIN}$  to  $T_{MAX}$  unless otherwise noted.

### Mode 1 - SHA Mode (cont.)

| Parameter <sup>1</sup>                        | B Version <sup>2</sup> | Units     | Conditions/Comments                        |

|-----------------------------------------------|------------------------|-----------|--------------------------------------------|

| DIGITAL OUTPUTS $(\overline{BUSY}, D_{OUT})$  |                        |           |                                            |

| Output Low Voltage                            | 0.4                    | V max     | DV <sub>CC</sub> = 5V. Sinking TBD mA      |

| Output High Voltage                           | 4.0                    | V min     | $DV_{CC} = 5V$ . Sourcing TBD $\mu A$      |

| Output Low Voltage                            | 0.4                    | V max     | $DV_{CC} = 3V$ . Sinking TBD mA            |

| Output High Voltage                           | 2.4                    | V min     | $DV_{CC} = 3V$ . Sourcing TBD $\mu A$      |

| Floating-State Leakage Current <sup>4</sup>   | TBD                    | μA max    |                                            |

| Floating-State Input Capacitance <sup>4</sup> | TBD                    | pF max    |                                            |

| POWER REQUIREMENTS                            |                        |           |                                            |

| Power-Supply Voltages                         |                        |           |                                            |

| $V_{DD}$                                      | +8/+16.5               | V min/max |                                            |

| $V_{ss}$                                      | -4.75/-16.5            | V min/max |                                            |

| $AV_{CC}$                                     | +4.75/+5.25            | V min/max |                                            |

| $DV_{CC}$                                     | +2.7/+5.25             | V min/max |                                            |

| Power-Supply Currents <sup>5</sup>            |                        |           |                                            |

| $I_{ m DD}$                                   | 22                     | mA typ    |                                            |

| $I_{SS}$                                      | 22                     | mA typ    |                                            |

| $\mathrm{AI}_{\mathrm{CC}}$                   | 54                     | mA typ    |                                            |

| $\mathrm{DI}_{\mathrm{cc}}$                   | < 1                    | mA max    |                                            |

| Power Dissipation <sup>5</sup>                | 600                    | mW typ    | $V_{DD}=10V$ , $V_{SS}=-5V$                |

| AC CHARACTERISTICS                            |                        |           |                                            |

| AC Crosstalk                                  | 2,5                    | nV-s max  |                                            |

| Output Settling Time                          | . 3                    | μs max    | 100pF Capacitive load                      |

| Acquisition Time                              | 16                     | μs max    | Acquire $V_{IN}$ to $\pm 0.012\%$ accuracy |

| Slew Rate                                     | - 1                    | V/µs typ  | 1 114                                      |

| Digital Feedthrough                           | 2.5                    | nV-s typ  |                                            |

| Digital Crosstalk                             | 2.5                    | nV-s typ  |                                            |

| TRACK MODE                                    |                        |           |                                            |

| Output PSRR                                   | TBD                    | dB        | V <sub>DD</sub> varied ±5%.                |

| -                                             | TBD                    | dB        | $V_{ss}$ varied $\pm 5\%$                  |

| Bandwidth                                     | TBD                    | kHz typ   |                                            |

#### NOTES:

<sup>&</sup>lt;sup>1</sup>See Terminology

<sup>&</sup>lt;sup>2</sup>B Version: Industrial temperature range -40°C. to +85°C.

<sup>&</sup>lt;sup>3</sup>Guaranteed by design and characterisation, not production tested

Outputs Unloaded. All figures are for the AD5564. The numbers for AD5532 are approx 50% of these.

Specifications subject to change without notice

$\begin{array}{l} \textbf{AD5532/64-SPECIFICATIONS} \ \ v_{\text{DD}} = +8 \text{V to } +16.5 \text{V}, \ v_{\text{SS}} = -4.75 \text{V to } -16.5 \text{V}; \ \text{AV}_{\text{CC}} = +4.75 \text{V to } +5.25 \text{V}; \ \text{DV}_{\text{CC}} \\ = +2.7 \text{V to } +5.25 \text{V}; \ \text{AGND} = \text{DGND} = \text{DAC}\_\text{GND} = \text{OV}; \ \text{Output Range from} \\ \end{array}$ Vss+2.2V to  $V_{DD}$  -2V. All specifications  $T_{MIN}$  to  $T_{MAX}$  unless otherwise noted.

### Mode 2 - DAC Mode

| Parameter <sup>1</sup>           | B Version <sup>2</sup> | Units                      | Conditions/Comments  |

|----------------------------------|------------------------|----------------------------|----------------------|

| DC PERFORMANCE                   |                        |                            |                      |

| Resolution                       | 14                     | Bits                       |                      |

| Integral Nonlinearity (INL)      | TBD                    | % of FSR typ               |                      |

| Differential Nonlinearity (DNL)  | ±1                     | LSB max                    | Guaranteed Monotonic |

| Offset Error                     | TBD                    | mV max                     |                      |

| Gain Error                       | TBD                    | % max                      |                      |

| Full-Scale Error                 | TBD                    | mV max                     |                      |

| Offset Error Temp Coeff          | TBD                    | μV/°C typ                  |                      |

| Gain Error Temp Coeff            | TBD                    | μV/°C typ                  |                      |

| Channel-to-Channel Matching      | TBD                    | % max                      |                      |

| AC CHARACTERISTICS               |                        |                            |                      |

| Output Settling Time             | TBD                    | μs typ                     |                      |

| OFFS_IN Settling Time            | TBD                    | μs typ                     |                      |

| Digital-to-Analog Glitch Impulse | TBD                    | nV-s typ                   |                      |

| Digital Crosstalk                | TBD                    | nV-s typ                   |                      |

| Analog Crosstalk                 | TBD                    | nV-s typ                   |                      |

| Total Harmonic Distortion (THD   | ) TBD                  | dB typ                     |                      |

| Output Noise Spectral Density    | TBD                    | nV/(Hz) <sup>1/2</sup> typ | &                    |

NOTES:

<sup>1</sup>See Terminology

Specifications subject to change without notice

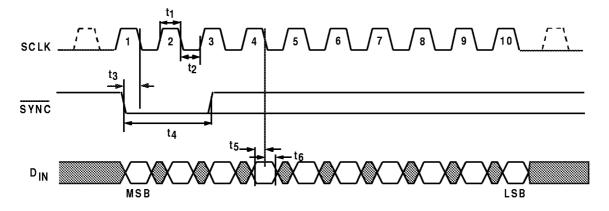

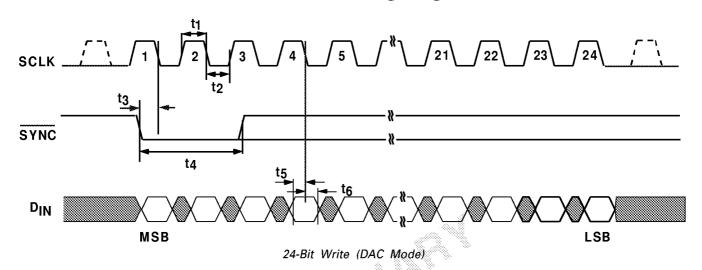

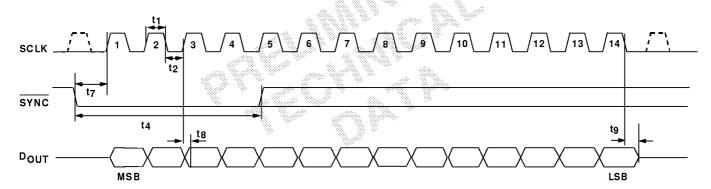

## **Timing Characteristics** Serial Interface

| Parameter <sup>1</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (B Version) | Units  | Conditions/Comments                                  |

|------------------------|----------------------------------------------------------|--------|------------------------------------------------------|

| $t_1$                  | 25                                                       | ns min | SCLK High Pulse Width                                |

| $t_2$                  | 25                                                       | ns min | SCLK Low Pulse Width                                 |

| $t_3$                  | 5                                                        | ns min | SYNC Falling Edge to SCLK Falling Edge Setup         |

|                        |                                                          |        | Time                                                 |

| $t_4$                  | TBD                                                      | ns min | SYNC Low Time                                        |

| t <sub>5</sub>         | 10                                                       | ns min | D <sub>IN</sub> Setup Time                           |

| $t_6$                  | 5                                                        | ns min | D <sub>IN</sub> Hold Time                            |

| t <sub>7</sub>         | 5                                                        | ns min | SYNC Falling Edge to SCLK Rising Edge Setup Time     |

| $t_8^2$                | 10                                                       | ns max | SCLK Rising Edge to D <sub>OUT</sub> Valid           |

| $t_9^2$                | 20                                                       | ns max | SCLK Falling Edge to D <sub>OUT</sub> High Impedance |

<sup>&</sup>lt;sup>2</sup>B version: Industrial temperature range -40°C. to +85°C.

<sup>&</sup>lt;sup>3</sup>Guaranteed by design and characterisation, not production tested

<sup>&</sup>lt;sup>1</sup>See Interface Timing Diagrams on following pages

<sup>&</sup>lt;sup>2</sup>These numbers are measured with the load circuit of Figure x

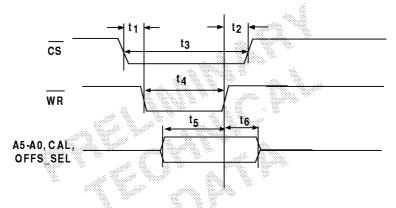

### **Parallel Interface**

| Parameter <sup>1</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (B Version) | Units  | Conditions/Comments                                                            |

|------------------------|----------------------------------------------------------|--------|--------------------------------------------------------------------------------|

| $t_1$                  | 0                                                        | ns min | CS to WR Setup Time                                                            |

| $\mathbf{t}_2$         | 0                                                        | ns min | CS to WR Hold Time                                                             |

| $t_3$                  | 50                                                       | ns min | CS Pulse Width Low                                                             |

| $t_4$                  | 50                                                       | ns min | WR Pulse Width Low                                                             |

| $t_5$                  | 20                                                       | ns min | A5-A0, CAL, OFFS_SEL to WR Setup Time                                          |

| $t_6$                  | 0                                                        | ns min | A5-A0, CAL, OFFS_SEL to $\overline{\mathbb{W}}\overline{\mathbb{R}}$ Hold Time |

#### NOTES:

# **Parallel Interface Timing Diagram**

## **Serial Interface Timing Diagrams**

10-Bit Write (SHA Mode and Both Readback Modes)

\_5\_ REV. PrE

<sup>&</sup>lt;sup>1</sup>See Interface Timing Diagrams below

### **Serial Interface Timing Diagrams**

14-Bit Read(Both Readback

| AGND to DGNDTBD                                          |

|----------------------------------------------------------|

| Short-Circuit CurrentTBD mA                              |

| Operating Temperature Range                              |

| Industrial (B Version)40°C to +85°C                      |

| Storage Temperature Range65°C to +150°C                  |

| Junction Temperature (T <sub>1</sub> max)+150°C          |

| BGA Package,                                             |

| Power Dissipation( $T_I$ max - $T_A$ )/ $\theta_{IA}$ mW |

| θ <sub>IA</sub> Thermal Impedance28°C /W                 |

| Solder Ball Temperature, SolderingTBD °C.                |

| NOTES:                                                   |

<sup>1</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Transient currents of up to 100mA will not cause SCR latch-up

#### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD5532/64 devices feature proprietary ESD protection circuitry, permanent damage may still occur on these devices if they are subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### Terminology SHA Mode

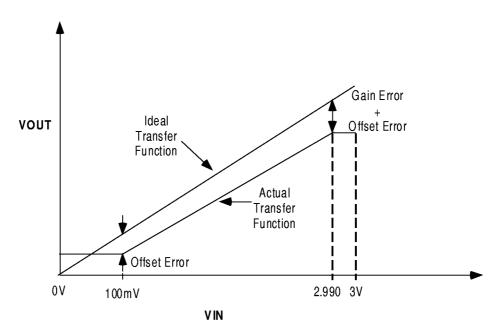

#### VIN to VOUT Nonlinearity

This is a measure of the maximum deviation from a straight line passing through the endpoints of the  $V_{\rm IN}$  vs.  $V_{\rm OUT}$  transfer function. It is expressed as a percentage of the full-scale span.

#### Offset Error

This is a measure of the output error when  $V_{IN} = 100 \text{mV}$ . Ideally, with  $V_{IN}=100 \text{mV}$ :

$V_{OUT}$ = 350mV-2.5\* $V_{OFFSET}$

Offset error is a measure of the difference between  $V_{\rm OUT}$  (actual) and  $V_{\rm OUT}$  (ideal). It is expressed in mV.

#### Full-Scale Error

This is a measure of the output error when  $V_{IN} = V_{REF}$ . Ideally, with  $V_{IN}=V_{REF}$ :

$V_{OUT} = 3.5 \times V_{REF} - 2.5 \times V_{OFFSET}$

Full-scale error is a measure of the difference between  $V_{\rm OUT}$  (actual) and  $V_{\rm OUT}$  (ideal). It is expressed in mV.

#### Gain Error

This is a measure of the span error of the analog channel. It is the deviation in slope of the transfer function expressed in mV. It is calculated as:

Gain Error = Full-Scale error - Offset Error

#### Channel-to-Channel Matching

This is a measure of the difference between  $V_{\rm OUT}$  on any two channels if they acquire the same  $V_{\rm IN}$ . It is expressed as a percentage of the Full-Scale span.

#### Output Temp Coefficient

This is a measure of the change in analog output with changes in temperature. It is expressed in ppm/°C.

#### Output PSRR

Power-Supply Rejection Ratio (PSRR) is a measure of the change in analog output for a change in supply voltage ( $V_{DD}$  and  $V_{SS}$ ). It is expressed in dBs.  $V_{DD}$  and  $V_{SS}$  are varied  $\pm$  5%. For the PSRR measurement of OFFS\_OUT, the AV<sub>CC</sub> supply is varied  $\pm$  5%.

#### DC Crosstalk

This the DC change in the output level of one channel in response to a full-scale change in the output of all other channels. It is expressed in  $\mu V$ .

#### AC Crosstalk

This is the area of the glitch that occurs on the output of one channel while another channel is acquiring. It is expressed in nV-secs.

#### Output Settling Time

This is the time taken from when  $\overline{BUSY}$  goes high to when the output has settled to  $\pm$  0.012% ( $\pm$  0.5 LSB at 12 bits).

#### Acquisition Time

This is the time taken for the  $V_{\rm IN}$  input to be acquired. It is the length of time that  $\overline{BUSY}$  stays low.

#### Digital Feeedthrough

This is a measure of the impulse injected into the analog outputs from the digital control inputs when the part is not being written to, i.e.  $\overline{CS}/\overline{SYNC}$  is high. The digital inputs are toggled between all 0s and all 1s. The area of the glitch is expressed in nV-secs.

#### Digital Crosstalk

This is the area of the glitch transferred to the analog output while a digital word is being written to the part. The area of the glitch is expressed in nV-secs.

#### TRACK Mode Bandwidth

When  $\overline{TRACK}$  input is brought low, the input voltage on  $V_{IN}$  is not acquired. It is connected directly to the output buffer stage and the output voltage is:

$V_{OUT}$ = 3.5\* $V_{IN}$ -2.5\* $V_{OFFSET}$

$V_{IN}$  can, of course, be an AC waveform in which case the TRACK mode has a finite bandwidth. The bandwidth is the frequency at which the sine wave at the output falls to 3dB below the sine wave at the input (ignoring the gain factor).

### **DAC** Mode

#### Integral Nonlinearity (INL)

This is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is expressed as a percentage of Full-Scale span.

#### Differential Nonlinearity (DNL)

Differential Nonlinearity (DNL) is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified DNL of ±1 LSB maximum ensures monotonicity.

#### Offset Error

This is a measure of the output error with all zeroes loaded to the DAC. Ideally the output should be:

$V_{OUT} = 350 \text{mV} - 2.5 \text{*} V_{OFFSET}$

Offset error is a measure of the difference between  $V_{\rm OUT}$  (actual) and  $V_{\rm OUT}$  (ideal). It is expressed in mV.

#### Full-Scale Error

This is a measure of the output error with all ones loaded to the DAC. Ideally, the output should be:

$V_{OUT}$ = 3.5\* $V_{REF}$ -2.5\* $V_{OFFSET}$

Full-scale error is a measure of the difference between  $V_{\rm OUT}$  (actual) and  $V_{\rm OUT}$  (ideal). It is expressed in mV.

#### Gain Error

This is a measure of the span error of the DAC. It is the deviation in slope of the transfer function expressed in mV. It is calculated as:

Gain Error = Full-Scale error - Offset Error

\_7\_ REV. PrE

#### Channel-to-Channel Matching

This is a measure of the difference between  $V_{\text{OUT}}$  on any two DACs if they have the same digital code loaded to them. It is expressed as a percentage of the Full-scale span.

#### Output Settling Time

This is the time taken from when the last data bit is clocked into the DAC until the output has settled to within  $\pm$  0.012% ( $\pm$  0.5 LSB at 12 bits).

#### OFFS\_IN Settling Time

This is the time taken from a step change in input voltage on OFFS\_IN until the output has settled to within  $\pm$  0.012% ( $\pm$  0.5 LSB at 12 bits).

#### Digital-to-Analog Glitch Impulse

This is the area of the glitch injected into the analog output when the code in the DAC register changes state. It is specified as the area of the glitch in nV-secs when the digital code is changed by 1 LSB at the major carry transition (011...11 to 100...00).

#### Digital Crosstalk

This is the area of the glitch transferred to the analog output while a DAC code is being written to the part. The area of the glitch is expressed in nV-secs.

#### Analog Crosstalk

This the area of the glitch transferred to the output of one DAC due to a full-scale change in the output of another DAC. The area of the glitch is expressed in nV-secs.

#### **Total Harmonic Distortion**

This is the difference between an ideal sine-wave and a digitally constructed one using the DAC. The THD is a measure of the harmonics and noise present on the DAC output. It is measured in dBs.

Figure 1. SHA Transfer Function

#### PIN FUNCTION DESCRIPTION

### PIN NUMBERS

| Pin<br>No. | Mnemonic                                                                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | AGND (1-4)                                                                             | 4 Analog GND pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | $AV_{CC}$ (1-4)                                                                        | 4 Analog supply pins. Voltage range from +4.75V to +5.25V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | $V_{DD}$ (1-8)                                                                         | 8 $V_{\rm DD}$ supply pins. Voltage range from +8V to +16.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | V <sub>SS</sub> (1-8)                                                                  | 8 V <sub>ss</sub> supply pins. Voltage range from -4.75V to -16.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            | DGND (1-2)                                                                             | 2 Digital GND pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | DV <sub>CC</sub> (1-2)<br>DAC_GND (1-4)<br>REF IN 1                                    | 2 Digital supply pins. Voltage range from +2.7V to +5.25V.<br>Reference GND supply for all the DACs.<br>Reference voltage for channels 0-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | REF IN 1                                                                               | Reference voltage for channels 32-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | V <sub>OUT</sub> (0-63)                                                                | Analog output voltages from the 64 channels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | $V_{IN}$                                                                               | Analog input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | A5-A1 <sup>1</sup> , A0 <sup>2</sup>                                                   | Parallel Interface: 6 address pins for the 64 channels. A5=MSB of channel address, A0=LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | $\frac{CAL^{1}}{CS} / \frac{SYNC^{2}}{SYNC^{2}}$                                       | Parallel Interface: Control input which allows all 64 channels to acquire V <sub>IN</sub> simultaneously This pin is both the active low Chip Select pin for the parallel interface and the Frame Synchronisation pin for the serial interface.                                                                                                                                                                                                                                                                                                                                                              |

|            | $\overline{\mathbf{W}}\overline{\mathbf{R}}^{\scriptscriptstyle 1}$                    | Parallel Interface. Write pin. Active low. This is used in conjunction with the $\overline{CS}$ pin to address the device using the parallel interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | OFFSET_SEL <sup>1</sup>                                                                | Offset Select pin. This is activated when writing to the DAC which provides its output at the OFFS_OUT pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | SCLK <sup>2</sup><br>D <sub>IN</sub> <sup>2</sup>                                      | Serial Clock input for serial interface. This can operate up at clock speeds up to 20MHz. Data input for serial interface. Data must be valid onthe falling edge of SCLK                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | D <sub>OUT</sub>                                                                       | Output from the DAC registers for readback. Data is clocked out on the rising edge of SCLK and is valid on the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | SER/PAR¹                                                                               | This pin allows the user to select whether the serial or parallel interface will be used. If the pin is tied low, the parallel interface will be used. If it is tied high, the serial interface will be used.                                                                                                                                                                                                                                                                                                                                                                                                |

|            | OFFS_IN                                                                                | Offset input. The user can supply a voltage here to offset the output span. OFFS_OUT can also be tied to this pin if the user wants to drive this pin with the Offset Channel.                                                                                                                                                                                                                                                                                                                                                                                                                               |

|            | OFFS_OUT                                                                               | Offset output. This is the acquired offset voltage which can be tied to OFFS_IN to offset the span.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            | $\overline{\mathrm{B}}\overline{\mathrm{U}}\overline{\mathrm{S}}\overline{\mathrm{Y}}$ | This output tells the user when the input voltage is being acquired. It goes low during acquisition and returns high when the acquisition operation is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|            | TRACK/RESET <sup>2</sup>                                                               | If this input is held high, $V_{\rm IN}$ is acquired once the channel is addressed. While it is held low, the input to the gain/offset stage is switched directly to $V_{\rm IN}$ . The addressed channel begins to acquire $V_{\rm IN}$ on the rising edge of $\overline{\rm TRACK}$ . See $\overline{\rm TRACK}$ Input section for further information. This input can also be used as a means of resetting the complete device to its power-on-reset conditions. This is achieved by applying a low going pulse of between 50ns and 150ns to this pin. See section on RESET Function for further details. |

#### NOTES:

<sup>1</sup>Internal Pull-down devices on these logic inputs. Therfore, they can be left floating and will default to a logic low condition.

<sup>2</sup>Internal Pull-up devices on these logic inputs. Therfore, they can be left floating and will default to a logic high condition.

#### Circuit Description

The AD5532/64 can be thought of as consisting of an ADC and 32/64 DACs in a single package. The input voltage  $V_{\rm IN}$  is sampled and converted into a digital word. The digital result is loaded into one of the DAC registers and is converted (after the gain and offset in the output buffer) into an analog output voltage ( $V_{\rm OUT}0$  -  $V_{\rm OUT}$  63). Since the channel output voltage is effectively the output of a DAC there is no droop associated with it. As long as power is maintained to the device the output voltage will remain constant until this channel is addressed again.

To update a single channel's output voltage the required new voltage level is set up on the common input pin, V<sub>IN</sub>. The desired channel is then addressed via the parallel port or the serial port. When the channel address has been loaded, provided TRACK is high, the circuit begins to acquire the correct code to load to the DAC in order that the DAC output matches the voltage on V<sub>IN</sub>. At this stage the BUSY pin goes low and remains so until the acquistion is complete. The non-inverting input to the output buffer (gain and offset stage) is tied to V<sub>IN</sub> during the acquisition period to avoid spurious outputs while the DAC acquires the correct code. This is completed in 16 us max. The BUSY pin goes high at this stage. Also at this time the updated DAC output assumes control of the output voltage. The output voltage of the DAC is connected to the non-inverting input of the output buffer. The held voltage will remain on the output pin indefinitely, without drooping, as long as power is maintained to the device.

On power-on, all the DACs, including the offset channel, are loaded with zeroes. The outputs of the DACs are at 100mV and the outputs of the output buffers are at negative full-scale. If the OFFS\_IN pin is driven by the on-board offset channel, the outputs  $V_{\rm OUT}$ 0 to  $V_{\rm OUT}$ 63 are also at 100mV on power-on since OFFS\_IN = 100mV ( $V_{\rm OUT}$ =3.5\* $V_{\rm DAC}$ -2.5\* $V_{\rm OFFSET}$ =350mV-250mV=100mV).

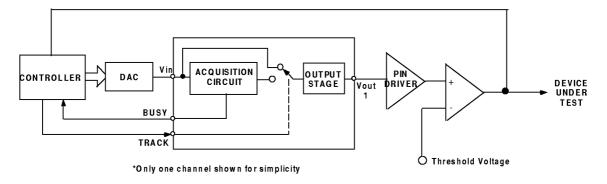

#### TRACK Input

In normal mode of operation,  $\overline{TRACK}$  is held high and the channel begins to acquire when it is addressed. However, if  $\overline{TRACK}$  is low when the channel is addressed then  $V_{IN}$  is switched to the output buffer and an acquisition on the channel will not occur until a rising edge of  $\overline{TRACK}$ . At this stage the  $\overline{BUSY}$  pin will go low

until the acquisition is complete at which point the DAC assumes control of the voltage to the output buffer and  $V_{\rm IN}$  is free to change again without affecting this output value.

This is useful in an application where the user wants to ramp up  $V_{\rm IN}$  until  $V_{\rm OUT}$  reaches a particular level (Figure 2).  $V_{\rm IN}$  doesn't need to be acquired continuously while it is ramping up.  $\overline{TRACK}$  can be kept low and only when  $V_{\rm OUT}$  has reached its desired voltage is  $\overline{TRACK}$  brought high. At this stage, the acquisition of  $V_{\rm IN}$  begins.

In the example shown, a desired voltage is required on the output of the pin driver. This voltage is represented by one input to a comparator. The microcontroller/microprocessor ramps up the input voltage on  $V_{\rm IN}$  through a DAC.  $\overline{TRACK}$  is kept low while the voltage on  $V_{\rm IN}$  ramps up so that  $V_{\rm IN}$  is not continually acquired. When the desired voltage is reached on the output of the pin driver, the comparator output switches. The  $\mu C/\mu P$  then knows what code is required to be input in order to get the desired voltage at the DUT. The  $\overline{TRACK}$  input is now brought high and the part begins to acquire  $V_{\rm IN}$ . At this stage  $\overline{BUSY}$  goes low until  $V_{\rm IN}$  has been acquired. Then the output buffer is switched from  $V_{\rm IN}$  to the output of the DAC.

#### Output Buffer Stage - Gain and Offset

The function of the output buffer stage is to translate the 0-3V output of the DAC to a useful range for ATE applications. This is done by gaining up the DAC output by 3.5 and offsetting the voltage by the voltage on OFFS\_IN pin. The following table shows how the output range relates to the Offset voltage supplied by the user.

$$V_{OUT} = 3.5 \times V_{DAC} - 2.5 \times V_{OFFSET}$$

$V_{\text{DAC}}$  is the output of the DAC and its range is 0-V<sub>REF</sub>.  $V_{\text{OFFSET}}$  is the voltage at the OFFS\_IN pin.

#### SAMPLE OUTPUT RANGES

| V <sub>OFFSET</sub> (V) | V <sub>DAC</sub> (V) | V <sub>OUT</sub> (V) |

|-------------------------|----------------------|----------------------|

| 1                       | 0 to 3               | -2.5 to 8            |

| 0.5                     | 0 to 3               | -1.25 to 9.25        |

$V_{\text{OUT}}$  is limited only by the headroom of the output amplifiers.

Figure 2. Typical ATE circuit using TRACK Input

#### Offset Voltage Channel

The offset voltage can be supplied externally by the user or it can be supplied by an additional DAC on the device itself. The offset voltage channel is used just like any other channel. The required offset voltage is set up on  $V_{\rm IN}$  and it is acquired by the DAC. The DAC output is connected directly to OFFS\_OUT. This offset voltage is used as the offset voltage for the 64 output amplifiers.

#### Reset Function

The reset function on the AD5532/64 can be used to reset all nodes on this device to their power-on-reset condition. This is implemented by applying a low going pulse of between 50ns and 150ns to the  $\overline{TRACK/RESET}$  pin on the device. If the applied pulse is less than 50ns it is taken as being a glitch and no operation takes place. If the applied pulse is wider than 150ns this pin adopts its track function on the selected channel,  $V_{\rm IN}$  is switched to the output buffer and an acquisition on the channel will not occur until a rising edge of  $\overline{TRACK}$ .

#### **INTERFACE**

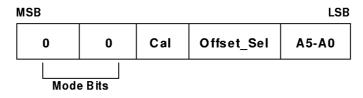

#### Serial Interface

The serial interface is controlled by 4 pins.  $\overline{SYNC}$ ,  $D_{IN}$ , SCLK: Standard 3-wire SPI interface pins. The  $\overline{SYNC}$  pin is shared with the  $\underline{CS}$  function of the parallel interface.

D<sub>OUT</sub>: Data Out pin for reading back the contents of the DAC registers. The data is clocked out on the rising edge of SCLK and is valid on the falling edge of SCLK.

The SER/PAR pin must also be tied high to enable the serial interface and to disable the parallel interface.

Mode bits: There are 4 different modes of operation. See below for descriptions.

Cal bit: This is used as a calibration instruction. When this is active, all 64 channels acquire  $V_{\rm IN}$  simultaneously.

Offset\_Sel bit: Used to address the offset voltage control channel.

A5-A0: Used to address any one of the 64 channels (A5 = MSB of address, A0=LSB).

DB13-DB0: These are used to write a 14-bit word into the addressed DAC register. Clearly, this is only valid when in DAC mode.

The AD5532/64 can be used in 4 different modes of operation. These modes are set by two Mode bits, the first 2 bits in the serial word.

#### MODES OF OPERATION

| Mode Bit 1 | Mode Bit 2 | Operating Mode       |

|------------|------------|----------------------|

| 0          | 0          | SHA Mode             |

| 0          |            | DAC Mode             |

| 1          | 0          | Acquire and Readback |

| 1          | 1          | Readback             |

### 1) SHA Mode:

Standard mode where a channel is addressed and that

channel acquires the voltage on  $V_{\rm IN}$ . This mode requires a 10-bit write (see figure below) to address the relevant channel ( $V_{\rm OUT}$ 0- $V_{\rm OUT}$ 63, Offset Channel or all channels).

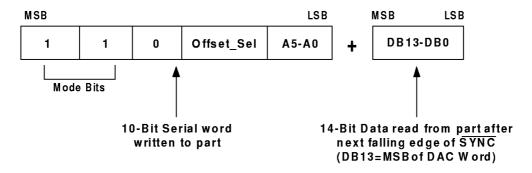

#### 2) DAC Mode:

In this mode, a particular DAC register can be written to directly. This mode requires the 10-bit write from the SHA mode plus an extra 14 bits to write to the 14-bit register of the DAC. Any one of the 64 DAC registers may be written to individually or they can all be loaded simultaneously.

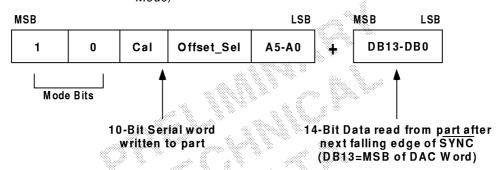

#### 3) Acquire and Readback Mode:

This mode allows the user to read back the data in a particular DAC register. The relevant DAC is addressed (10-bit write as with SHA mode) and  $V_{\rm IN}$  is acquired in typically 16us. Following the acquisition the next falling edge of  $\overline{\rm SYNC}$  clocks the data in the relevant DAC register out onto the  $D_{\rm OUT}$  line in a 14-bit serial format. The full acquisition time must elapse before the DAC register data can be clocked out.

#### 4) Readback

Again, this is a readback mode but no acquisition is performed. The relevant DAC is addressed (10-bit write) and on the next falling edge of  $\overline{\text{SYNC}}$ , the data in the relevant DAC register is clocked out onto the  $D_{\text{OUT}}$  line in a 14-bit serial format.

The serial write and read words can be seen in the figures below.

#### Digital Readback

This feature allows the user to readback the DAC register code of any of the DACs. This is useful if the system has been calibrated and the user wants to know what code in the DAC corresponds to a desired voltage on V<sub>OUT</sub>. If the user requires this voltage again, all he needs to do is to input the code directly to the DAC register without going through the acquisition sequence. The user can readback the DAC register contents through the serial interface and can write directly to the DAC, again through the serial interface.

#### Parallel Interface

The parallel interface is controlled by 10 pins.  $\overline{\text{CS}}$ : Active low package select pin. This pin is shared with the  $\overline{\text{SYNC}}$  function for the serial interface.  $\overline{\text{WR}}$ : Active low Write pin. The values on the address pins are latched on a rising edge of  $\overline{\text{WR}}$ .

A5-A0: 6 Address pins (A5=MSB of address, A0=LSB). These are used to address the relevant channel (out of a possible 64).

Offset\_Sel: Offset select pin. This has the same function as the Offset\_Sel bit in the serial interface. When it is activated, the offset voltage control channel is addressed. The address on A5-A0 is ignored in this case. Cal:Same functionality as the Cal bit in the serial interface (calibration instruction). When this pin is active, all

The SER/PAR bit must be tied low to enable the parallel interface and disable the serial interface.

64 channels acquire V<sub>IN</sub> simultaneously.

10-Bit Input Serial Write Word (SHA Mode)

24-Bit Input Serial Write Word (DAC Mode)

Input Serial Interface (Acquire and Readback Mode)

Input Serial Interface (Readback Mode)

-12- REV. PrE

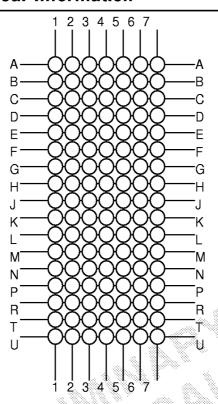

PBGA BALL CONFIGURATIONS

| PBGA<br>Number | Ball<br>Name                                                                           | PBGA<br>Number | Ball<br>Name                               | PBGA<br>Number | Ball<br>Name | PBGA<br>Number | Ball<br>Name |

|----------------|----------------------------------------------------------------------------------------|----------------|--------------------------------------------|----------------|--------------|----------------|--------------|

| A1             | VO26                                                                                   | E3             | AVSS8                                      | J5             | AGND3        | N7             | VO59         |

| A2             | $\overline{CS}/\overline{SYNC}$                                                        | E4             | AVSS7                                      | Ĵ6             | AGND4        | P1             | VO34         |

| A3             | A2                                                                                     | E5             | N/C                                        | J7             | VO3          | P2             | VO41         |

| A4             | A1                                                                                     | E6             | VO10                                       | K1             | VO31         | P3             | AVDD4        |

| A5             | A0                                                                                     | E7             | VO5                                        | K2             | DACGND1      | P4             | AVDD7        |

| A6             | $\overline{\mathrm{B}}\overline{\mathrm{U}}\overline{\mathrm{S}}\overline{\mathrm{Y}}$ | F1             | VO14                                       | K3             | DACGND2      | P5             | REF_IN1      |

| A7             | VO9                                                                                    | F2             | VO12                                       | K4             | DACGND3      | P6             | VO55         |

| B1             | VO25                                                                                   | F3             | AVSS6                                      | K5             | DACGND4      | P7             | VO62         |

| B2             | $\overline{\mathbf{W}}\overline{\mathbf{R}}$                                           | F4             | AVSS5                                      | K6             | AIN          | R1             | VO35         |

| В3             | SCLK                                                                                   | F5             | DVCC1                                      | K7             | VO2          | R2             | VO40         |

| B4             | SDIN                                                                                   | F6             | DVCC2                                      | L1             | VO32         | R3             | VO43         |

| B5             | SDOUT                                                                                  | F7             | VO4                                        | L2             | AVCC1        | R4             | VO46         |

| B6             | OFFSEL                                                                                 | G1             | VO16                                       | L3             | AVCC2        | R5             | VO63         |

| B7             | VO8                                                                                    | G2             | OFFS_IN                                    | L4             | AVCC3        | R6             | VO54         |

| C1             | VO24                                                                                   | G3             | OFFS_OUT                                   | L5             | AVCC4        | R7             | VO58         |

| C2             | VO22                                                                                   | G4             | AVSS4                                      | L6             | VO0          | T1             | VO37         |

| C3             | A5                                                                                     | G5             | $SER/\overline{P}\overline{A}\overline{R}$ | L7             | VO1          | T2             | VO39         |

| C4             | A4                                                                                     | G6             | VO15                                       | M 1            | VO27         | Т3             | VO49         |

| C5             | A3                                                                                     | G7             | VO17                                       | M2             | AVDD1        | T4             | VO48         |

| C6             | VO13                                                                                   | H1             | VO18                                       | M3             | AVDD2        | T5             | VO45         |

| C7             | VO7                                                                                    | H2             | AVSS1                                      | M4             | AVDD5        | Т6             | VO53         |

| D1             | VO23                                                                                   | H3             | AVSS2                                      | M 5            | AVDD8        | T7             | VO57         |

| D2             | VO21                                                                                   | H4             | AVSS3                                      | M 6            | VO60         | U1             | VO36         |

| D3             | CAL                                                                                    | H5             | TRACK/RESET                                | M7             | VO61         | U2             | VO38         |

| D4             | DGND1                                                                                  | H6             | VO19                                       | N1             | VO33         | U3             | VO50         |

| D5             | DGND2                                                                                  | H7             | VO51                                       | N2             | VO42         | U4             | VO47         |

| D6             | VO11                                                                                   | J1             | VO30                                       | N3             | AVDD3        | U5             | VO44         |

| D7             | VO6                                                                                    | J2             | VO28                                       | N4             | AVDD6        | U6             | VO52         |

| E1             | VO29                                                                                   | J3             | AGND1                                      | N5             | REF_OUT      | U7             | VO56         |

| E2             | VO20                                                                                   | J 4            | AGND2 -13-                                 | N 6            | REF_IN2      |                | REV. PrE     |