# MC6802 MC6808 MC6802NS

### MICROPROCESSOR WITH CLOCK AND OPTIONAL RAM

The MC6802 is a monolithic 8-bit microprocessor that contains all the registers and accumulators of the present MC6800 plus an internal clock oscillator and driver on the same chip. In addition, the MC6802 has 128 bytes of on-board RAM located at hex addresses \$0000 to \$007F. The first 32 bytes of RAM, at hex addresses \$0000 to \$001F, may be retained in a low power mode by utilizing VCC standby; thus, facilitating memory retention during a power-down situation.

The MC6802 is completely software compatible with the MC6800 as well as the entire M6800 family of parts. Hence, the MC6802 is expandable to 64K words.

The MC6802NS is identical to the MC6802 without standby RAM feature. The MC6808 is identical to the MC6802 without on-board RAM.

- On-Chip Clock Circuit

- 128 x 8 Bit On-Chip RAM

- 32 Bytes of RAM are Retainable

- Software-Compatible with the MC6800

- Expandable to 64K Words

- Standard TTL-Compatible Inputs and Outputs

- 8-Bit Word Size

- 16-Bit Memory Addressing

- Interrupt Capability

### MOS

(N-CHANNEL, SILICON-GATE, DEPLETION LOAD)

MICROPROCESSOR

WITH CLOCK AND OPTIONAL RAM

### ORDERING INFORMATION

| Package Type | Frequency (MHz) | Temperature   | Order Number |

|--------------|-----------------|---------------|--------------|

| Ceramic      | 1.0             | 0°C to 70°C   | MC6802L      |

| L Suffix     | 1.0             | -40°C to 85°C | MC6802CL     |

|              | 1.0             | 0°C to 70°C   | MC6802NSL    |

|              | 1.0             | 0°C to 70°C   | MC6808L      |

|              | 1.5             | 0°C to 70°C   | MC68A02L     |

|              | 1.5             | -40°C to 85°C | MC68A02CL    |

|              | 1.5             | 0°C to 70°C   | MC68A08L     |

|              | 2.0             | 0°C to 70°C   | MC68B02L     |

|              | 2.0             | 0°C to 70°C   | MC68B08L     |

| Plastic      | 1.0             | 0°C to 70°C   | MC6802P      |

| P Suffix     | 1.0             | -40°C to 85°C | MC6802CP     |

|              | 1.0             | 0°C to 70°C   | MC6802NSP    |

|              | 1.0             | 0°C to 70°C   | MC6808P      |

|              | 1.5             | 0°C to 70°C   | MC68A02P     |

|              | 1.5             | 40°C to 85°C  | MC68A02CP    |

|              | 1.5             | 0°C to 70°C   | MC68A08P     |

|              | 2.6             | 0°C to 70°C   | MC68B02P     |

|              | 2.0             | 0°C to 70°C   | MC68B08P     |

|                          | PIN ASSIGN | MENT                        |

|--------------------------|------------|-----------------------------|

| ٧ss                      | 1.         | 40 RESET                    |

| HALT                     | 2          | 39 DEXTAL                   |

| MR                       | 3          | 38 XTAL                     |

| īRO <b>L</b>             | 4          | 37 <b>]</b> E               |

| VMA                      | 5          | 36 T RE**                   |

| NMI                      | 6          | 35 V <sub>CC</sub> Standby* |

| ВА                       | 7          | 34 <b>]</b> R/₩             |

| v <sub>cc</sub> <b>t</b> | 8          | 33 <b>1</b> D0              |

| A0 <b>[</b>              | 9          | 32 <b>1</b> D1              |

| A1 <b>[</b>              | 10         | 31 <b>I</b> D2              |

| A2 <b>[</b>              | 11         | 30 <b>p</b> D3              |

| A3 <b>[</b>              | 12         | 29 D4                       |

| A4 <b>[</b>              | 13         | 28 D5                       |

| . A5 🕻                   | 14         | 27 D6                       |

| A6 <b>[</b>              | 15         | 26 D7                       |

| A7 🕻                     | 16         | 25 1 A15                    |

| A8 🕻                     | 17         | 24 A14                      |

| A9 <b>[</b>              | 18         | 23 A13                      |

| A10 🕻                    | 19         | 22 A12                      |

| A11                      |            | 21 V <sub>SS</sub>          |

\*Pin 35 must be tied to 5 V on the MC6802NS \*\*Pin 36 must be tied to ground for the MC6808

#### TYPICAL MICROCOMPUTER Vcc IRO Counter/ MC6846 BECE. Timer I/O ROM, I/O, Timer MR VMA HALT RESET VMA Clock RE 2 k Bytes ROM R/W R/W<sub>MC6802</sub> NM 10 I/O Lines 3 Lines Timer Parallel MPU 1/0 D0-D7 D0-D7 **FXTAI** A0-A10 A0-A15 XTA Control A0-A15 CS1 CP1

This block diagram shows a typical cost effective microcomputer. The MPU is the center of the microcomputer system and is shown in a minimum system interfacing with a ROM combination chip. It is not intended that this system be limited to this function but that it be expandable with other parts in the M6800 Microcomputer family.

### MAXIMUM RATINGS

| Rating                                                                                                                  | Symbol           | Value                                          | Unit |

|-------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------|------|

| Supply Voltage                                                                                                          | V <sub>CC</sub>  | -0.3 to $+7.0$                                 | V    |

| Input Voltage                                                                                                           | V <sub>in</sub>  | -0.3 to +7.0                                   | ٧    |

| Operating Temperature Range<br>MC6802, MC680A02, MC680B02<br>MC6802C, MC680A02C<br>MC6802NS<br>MC680B, MC68A0B, MC68B08 | ТД               | 0 to +70<br>-40 to +85<br>0 to +70<br>0 to +70 | °C   |

| Storage Temperature Range                                                                                               | T <sub>stg</sub> | -55 to +150                                    | °C   |

This input contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this highimpedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either VSS or VCC).

### THERMAL CHARACTERISTICS

| Characteristic                                           | Symbol | Value | Unit |

|----------------------------------------------------------|--------|-------|------|

| Average Thermal Resistance (Junction to Ambient) Plastic |        | 100   |      |

| Ceramic                                                  | θJA    | 50    | °C/W |

### POWER CONSIDERATIONS

The average chip-junction temperature, TJ, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \circ \theta_{JA}) \tag{1}$$

Where:

TA = Ambient Temperature, °C

θ JA = Package Thermal Resistance, Junction-to-Ambient, °C/W

PD = PINT + PPORT

PINT=ICC×VCC, Watts - Chip Internal Power

PPORT=Port Power Dissipation, Watts - User Determined

For most applications PPORT

PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$P_D = K + (T_J + 273^{\circ}C)$

(2) Solving equations 1 and 2 for K gives:

$K = PD^{\bullet}(T_A + 273^{\circ}C) + \theta JA^{\bullet}PD^2$

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring PD (at equilibrium) for a known TA. Using this value of K the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

3-180

DC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5.0 Vdc ±5%, V<sub>SS</sub> = 0, T<sub>A</sub> = 0 to 70°C, unless otherwise noted)

| Characteristic                                                                                                   |                                                 | Symbol                              | Min                                                                  | Тур         | Max                  | Unit |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|-------------|----------------------|------|

| Input High Voltage                                                                                               | Logic, EXTAL<br>RESET                           | VIH                                 | V <sub>SS</sub> +2.0<br>V <sub>SS</sub> +4.0                         | _           | Vcc<br>Vcc           | ٧    |

| Input Low Voltage                                                                                                | Logic, EXTAL, RESET                             | VIL                                 | V <sub>SS</sub> -0.3                                                 | _           | V <sub>SS</sub> +0.8 | ٧    |

| input Leakage Current (Vin = 0 to 5.25 V, VCC = max)                                                             | Logic                                           | lin                                 | -                                                                    | 1.0         | 2.5                  | μА   |

| Output High Voltage  (ILoad = - 205 µA, VCC = min)  (ILoad = - 145 µA, VCC = min)  (ILoad = - 100 µA, VCC = min) | D0-D7<br>A0-A15, R/ <del>W</del> , VMA, E<br>BA | ∨он                                 | V <sub>SS</sub> +2.4<br>V <sub>SS</sub> +2.4<br>V <sub>SS</sub> +2.4 | _<br>_<br>_ | -<br>-               | v    |

| Output Low Voltage (ILoad = 1.6 mA, VCC = min)                                                                   |                                                 | VOL                                 | _                                                                    | _           | VSS+0.4              | ٧    |

| Internal Power Dissipation (Measured at TA = 0°C)                                                                |                                                 | PINT                                |                                                                      | 0.750       | 1.0                  | W    |

| V <sub>CC</sub> Standby                                                                                          | Power Down<br>Power Up                          | V <sub>SBB</sub><br>V <sub>SB</sub> | 4.0<br>4.75                                                          | <u>-</u>    | 5.25<br>5.25         | ٧    |

| Standby Current                                                                                                  |                                                 | <sup>1</sup> SBB                    | +                                                                    | _           | B.0                  | mA   |

| Capacitance $f$<br>( $V_{in} = 0$ , $T_{iA} = 25$ °C, $f = 1.0$ MHz)                                             | D0-D7<br>Logic Inputs, EXTAL                    | C <sub>in</sub>                     | -                                                                    | 10<br>6.5   | 12.5<br>10           | рF   |

|                                                                                                                  | A0-A15, R/W, VMA                                | Cout                                | -                                                                    | -           | 12                   | pF   |

<sup>\*</sup>In power-down mode, maximum power dissipation is less than 42 mW. #Capacitances are periodically sampled rather than 100% tested.

### **CONTROL TIMING** ( $V_{CC} = 5.0 \text{ V } \pm 5\%$ , $V_{SS} = 0$ , $T_A = T_L$ to $T_H$ , unless otherwise noted)

| Characteristics                                                                                                                               | Symbol                | MC68     | 3802<br>102NS<br>3808 |          | 8A02<br>8A08 | MC6<br>MC6 | Unit    |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|-----------------------|----------|--------------|------------|---------|----------|

|                                                                                                                                               |                       | Min      | Max                   | Min      | Max          | Min        | Max     | <u> </u> |

| Frequency of Operation                                                                                                                        | f <sub>o</sub>        | 0.1      | 1.0                   | 0.1      | 1.5          | 0.1        | 2.0     | MHz      |

| Crystal Frequency                                                                                                                             | fXTAL                 | 1.0      | 4.0                   | 1.0      | 6.0          | 1.0        | 8.0     | MHz      |

| External Oscillator Frequency                                                                                                                 | 4xf <sub>O</sub>      | 0.4      | 4.0                   | 0.4      | 6.0          | 0.4        | 8.0     | MHz      |

| Crystal Oscillator Start Up Time                                                                                                              | trc                   | 100      | -                     | 100      | _            | 100        | _       | ms       |

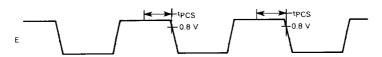

| Processor Controls (HALT, MR, RE, RESET, IRQ NMI) Processor Control Setup Time Processor Control Rise and Fall Time (Does Not Apply to RESET) | tPCS<br>tPCr,<br>tPCf | 200<br>– | -<br>100              | 140<br>— | -<br>100     | 110<br>–   | <br>100 | ns<br>ns |

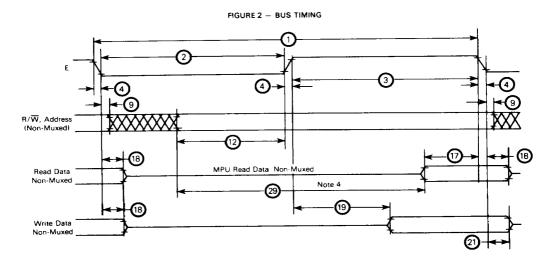

#### BUS TIMING CHARACTERISTICS

| ldent.<br>Number | Characteristic                                 | Symbol           | MC68<br>MC68 |          |       | 8A02<br>8A08 |         | 8B02<br>8B08   | Unit |

|------------------|------------------------------------------------|------------------|--------------|----------|-------|--------------|---------|----------------|------|

| Number           |                                                |                  | Min          | Max      | Min   | Max          | Min     | Max            |      |

| 1                | Cycle Time                                     | ¹cyc             | 1.0          | 10       | 0.667 | 10           | 0.5     | 10             | μS   |

| 2                | Pulse Width, E Low                             | PWEL             | 450          | 5000     | 280   | 5000         | 210     | 5000           | ns   |

| 3                | Pulse Width, E High                            | PWEH             | 450          | 9500     | 280   | 9700         | 220     | 9700           | ns   |

| 4                | Clock Rise and Fall Time                       | tr. If           | -            | 25       | _     | 25           |         | 25             | ns   |

| 9                | Address Hold Time*                             | tAH.             | 20           | -        | 20    | 1            | 20      |                | ns   |

| 12               | Non-Muxed Address Valid Time to E (See Note 5) | tAV1<br>tAV2     | 160<br>-     | -<br>270 | 100   | -            | 50<br>- | <i>-</i><br> - | ns   |

| 17               | Read Data Setup Time                           | <sup>†</sup> DSR | 100          | _        | 70    |              | 60      | _              | ns   |

| 18               | Read Data Hold Time                            | †DHR             | 10           | -        | 10    | -            | 10      | _              | ns   |

| 19               | Write Data Delay Time                          | tDDW             |              | 225      | -     | 170          | -       | 160            | ns   |

| 21               | Write Data Hold Time*                          | tDHW             | 30           |          | 20    | _            | 20      |                | ns   |

| 29               | Usable Access Time (See Note 4)                | †ACC             | 535          | _        | 335   | -            | 235     | -              | ns   |

<sup>\*</sup> Address and data hold times are periodically tested rather than 100% tested.

### NOTES:

- Voltage levels shown are V<sub>L</sub>≤0.4 V, V<sub>H</sub>≥2.4 V, unless otherwise specified.

- 2. Measurement points shown are 0.8 V and 2.0 V, unless otherwise noted.

- 3. All electricals shown for the MC6802 apply to the MC6802NS and MC6808, unless otherwise noted.

- 4. Usable access time is computed by: 12+3+4-17.

- If programs are not executed from on-board RAM, TAV1 applies. If programs are to be stored and executed from on-board RAM, TAV2 applies. For normal data storage in the on-board RAM, this extended delay does not apply. Programs cannot be executed from on-board RAM when using A and B parts (MC68A02, MC68A08, MC68B08). On-board RAM can be used for data storage with all parts.

- 6. All electrical and control characteristics are referenced from:  $T_L = 0$  °C minimum and  $T_H = 70$  °C maximum.

3-183

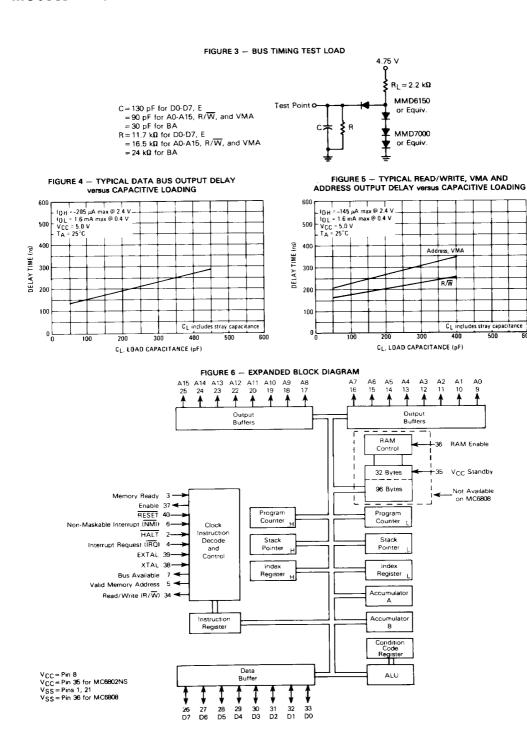

### MPU REGISTERS

A general block diagram of the MC6802 is shown in Figure 6. As shown, the number and configuration of the registers are the same as for the MC6800. The 128 × 8-bit RAM\* has been added to the basic MPU. The first 32 bytes can be retained during power-up and power-down conditions via the RE signal.

The MC6802NS is identical to the MC6802 except for the standby feature on the first 32 bytes of RAM. The standby feature does not exist on the MC6802NS and thus pin 35 must be tied to 5 V.

The MC6808 is identical to the MC6802 except for onboard RAM. Since the MC6808 does not have on-board RAM pin 36 must be tied to ground allowing the processor to utilize up to 64K bytes of external memory.

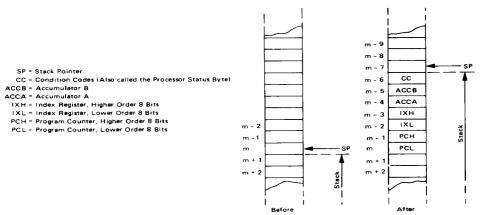

The MPU has three 16-bit registers and three 8-bit registers available for use by the programmer (Figure 7).

#### PROGRAM COUNTER

The program counter is a two byte (16-bit) register that points to the current program address.

#### STACK POINTER

The stack pointer is a two byte register that contains the address of the next available location in an external push-down/pop-up stack. This stack is normally a random access

read/write memory that may have any location (address) that is convenient. In those applications that require storage of information in the stack when power is lost, the stack must be non-volatile.

#### INDEX REGISTER

The index register is a two byte register that is used to store data or a 16-bit memory address for the indexed mode of memory addressing.

#### **ACCUMULATORS**

The MPU contains two 8-bit accumulators that are used to hold operands and results from an arithmetic logic unit (ALU).

#### CONDITION CODE REGISTER

The condition code register indicates the results of an Arithmetic Logic Unit operation: Negative (N), Zero (Z), Overflow (V), Carry from bit 7 (C), and Half Carry from bit 3 (H). These bits of the Condition Code Register are used as testable conditions for the conditional branch instructions. Bit 4 is the interrupt mask bit (I). The unused bits of the Condition Code Register (b6 and b7) are ones.

Figure 8 shows the order of saving the microprocessor status within the stack.

ACCA Accumulator A ACCE Accumulator B ıx Index Register PC Program Counter SP Stack Pointer Condition Codes 1 1 H I N Z V C Carry (From Bit 7) Overflow Zero Negative Interrupt Half Carry (From Bit 3)

FIGURE 7 - PROGRAMMING MODEL OF THE MICROPROCESSING UNIT

3-184

<sup>\*</sup>If programs are not executed from on-board RAM, TAV1 applies. If programs are to be stored and executed from on-board RAM, TAV2 applies. For normal data storage in the on-board RAM, this extended delay does not apply. Programs cannot be executed from on-board RAM when using A and B parts (MC68A02, MC68A08, MC68B02, and MC68B08). On-board RAM can be used for data storage with all parts.

FIGURE 8 - SAVING THE STATUS OF THE MICROPROCESSOR IN THE STACK

### MPU SIGNAL DESCRIPTION

Proper operation of the MPU requires that certain control and timing signals be provided to accomplish specific functions and that other signal lines be monitored to determine the state of the processor. These control and timing signals are similar to those of the MC6800 except that TSC, DBC, d1, \$\phi\_2\$ input, and two unused pins have been eliminated, and the following signal and timing lines have been added:

RAM Enable (RE)

Crystal Connections EXTAL and XTAL

Memory Ready (MR)

VCC Standby

Enable  $\phi2$  Output (E)

The following is a summary of the MPU signals:

### ADDRESS BUS (A0-A15)

Sixteen pins are used for the address bus. The outputs are capable of driving one standard TTL load and 90 pF. These lines do not have three-state capability.

### DATA BUS (D0-D7)

Eight pins are used for the data bus. It is bidirectional, transferring data to and from the memory and peripheral devices. It also has three-state output buffers capable of driving one standard TTL load and 130 pF.

Data bus will be in the output mode when the internal RAM is accessed and RE will be high. This prohibits external data entering the MPU. It should be noted that the internal RAM is fully decoded from \$0000 to \$007F. External RAM at \$0000 to \$007F must be disabled when internal RAM is accessed.

### HALT

When this input is in the low state, all activity in the machine will be halted. This input is level sensitive. In the HALT mode, the machine will stop at the end of an instruc-

tion, bus available will be at a high state, valid memory address will be at a low state. The address bus will display the address of the next instruction.

To ensure single instruction operation, transition of the HALT line must occur tpcs before the falling edge of E and the HALT line must go high for one clock cycle.

HALT should be tied high if not used. This is good engineering design practice in general and necessary to ensure proper operation of the part.

### READ/WRITE (R/W)

This TTL-compatible output signals the peripherals and memory devices whether the MPU is in a read (high) or write (low) state. The normal standby state of this signal is read (high). When the processor is halted, it will be in the read state. This output is capable of driving one standard TTL load and 90 pF.

### **VALID MEMORY ADDRESS (VMA)**

This output indicates to peripheral devices that there is a valid address on the address bus. In normal operation, this signal should be utilized for enabling peripheral interfaces such as the PIA and ACIA. This signal is not three-state. One standard TTL load and 90 pF may be directly driven by this active high signal.

BUS AVAILABLE (BA) — The bus available signal will normally be in the low state; when activated, it will go to the high state indicating that the microprocessor has stopped and that the address bus is available (but not in a three-state condition). This will occur if the HALT line is in the low state or the processor is in the WAIT state as a result of the execution of a WAIT instruction. At such time, all three-state output drivers will go to their off-state and other outputs to their normally inactive level. The processor is removed from the

. . .

WAIT state by the occurrence of a maskable (mask bit != 0) or nonmaskable interrupt. This output is capable of driving one standard TTL load and 30 pF.

#### INTERRUPT REQUEST (IRQ)

A low level on this input requests that an interrupt sequence be generated within the machine. The processor will wait until it completes the current instruction that is being excuted before it recognizes the request. At that time, if the interrupt mask bit in the condition code register is not set, the machine will begin an interrupt sequence. The index register, program counter, accumulators, and condition code register are stored away on the stack. Next the MPU will respond to the interrupt request by setting the interrupt mask bit high so that no further interrupts may occur. At the end of the cycle, a 16-bit vectoring address which is located in memory locations \$FFF8 and \$FFF9 is loaded which causes the MPU to branch to an interrupt routine in memory.

The HALT line must be in the high state for interrupts to be serviced. Interrupts will be latched internally while HALT

A nominal 3 kΩ pullup resistor to VCC should be used for wire-OR and optimum control of interrupts. IRQ may be tied directly to VCC if not used.

#### RESET

This input is used to reset and start the MPU from a power-down condition, resulting from a power failure or an initial start-up of the processor. When this line is low, the MPU is inactive and the information in the registers will be lost. If a high level is detected on the input, this will signal the MPU to begin the restart sequence. This will start execu-

tion of a routine to initialize the processor from its reset condition. All the higher order address lines will be forced high. For the restart, the last two (\$FFFE, \$FFFF) locations in memory will be used to load the program that is addressed by the program counter. During the restart routine, the interrupt mask bit is set and must be reset before the MPU can be interrupted by IRQ. Power-up and reset timing and powerdown sequences are shown in Figures 9 and 10, respectively.

RESET, when brought low, must be held low at least three clock cycles. This allows adequate time to respond internally to the reset. This is independent of the tro power-up reset that is required.

When RESET is released it must go through the low-tohigh threshold without bouncing, oscillating, or otherwise causing an erroneous reset (less than three clock cycles). This may cause improper MPU operation until the next valid

### NON-MASKABLE INTERRUPT (NMI)

A low-going edge on this input requests that a nonmaskable interrupt sequence be generated within the processor. As with the interrupt request signal, the processor will complete the current instruction that is being executed before it recognizes the NMI signal. The interrupt mask bit in the condition code register has no effect on NMI

The index register, program counter, accumulators, and condition code registers are stored away on the stack. At the end of the cycle, a 16-bit vectoring address which is located in memory locations \$FFFC and \$FFFD is loaded causing the MPU to branch to an interrupt service routine in memory.

A nominal 3 kn pullup resistor to VCC should be used for wire-OR and optimum control of interrupts. NMI may be tied

t<sub>fC</sub> RESET Option 1 (See Note Below) tro: RESET Option 2 (See Figure 10 for Power-down Condition) tpc:

FIGURE 9 - POWER-UP AND RESET TIMING

NOTE: If option 1 is chosen, RESET and RE pins can be tied together

directly to VCC if not used.

Inputs IRO and NMI are hardware interrupt lines that are sampled when E is high and will start the interrupt routine on a low E following the completion of an instruction.

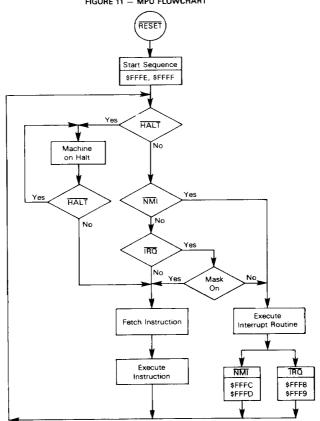

Figure 11 is a flowchart describing the major decision paths and interrupt vectors of the microprocessor. Table 1 gives the memory map for interrupt vectors.

TABLE 1 — MEMORY MAP FOR INTERRUPT VECTORS

| Vec    | tor    | Description            |

|--------|--------|------------------------|

| MS     | LS     | Description            |

| \$FFFE | \$FFFF | Restart                |

| \$FFFC | \$FFFD | Non-Maskable Interrupt |

| \$FFFA | \$FFFB | Software Interrupt     |

| \$FFFB | \$FFF9 | Interrupt Request      |

FIGURE 10 — POWER-DOWN SEQUENCE

VCC

E

ICPS

VIH

VIL

3 Cycles

FIGURE 11 - MPU FLOWCHART

FIGURE 23 - PROGRAM FLOW FOR INTERRUPTS

3-168

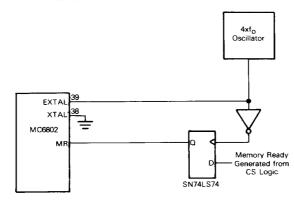

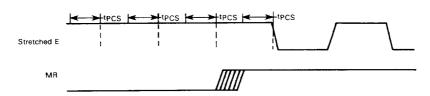

FIGURE 14 - MEMORY READY SYNCHRONIZATION

FIGURE 15 - MR NEGATIVE SETUP TIME REQUIREMENT

### E Clock Stretch

The E clock will be stretched at end of E high of the cycle during which MR negative meets the tpcs setup time. The tpcs setup time is referenced to the fall of E. If the tpcs setup time is not met, E will be stretched at the end of the next E-high ½ cycle. E will be stretched in integral multiples of ½ cycles.

### Resuming E Clocking

The E clock will resume normal operation at the end of the ½ cycle during which MR assertion meets the tpcs setup time. The tpcs setup time is referenced to transitions of E were it not stretched. If tpcs setup time is not met, E will fall at the second possible transition time after MR is asserted. There is no direct means of determining when the tpcs references occur, unless the synchronizing circuit of Figure 14 is used.

#### RAM ENABLE (RE - MC6802 + MC6802NS ONLY)

A TTL-compatible RAM enable input controls the on-chip RAM of the MC6802. When placed in the high state, the on-chip memory is enabled to respond to the MPU controls. In the low state, RAM is disabled. This pin may also be utilized to disable reading and writing the on-chip RAM during a power-down situation. RAM Enable must be low three cycles before VCC goes below 4.75 V during power-down. RAM enable must be tied low on the MC6808. RE should be tied to the correct high or low state if not used.

#### EXTAL AND XTAL

These inputs are used for the internal oscillator that may be crystal controlled. These connections are for a parallel resonant fundamental crystal (see Figure 12). (AT-cut.) A divide-by-four circuit has been added so a 4 MHz crystal may be used in lieu of a 1 MHz crystal for a more cost-effective system. An example of the crystal circuit layout is shown in Figure 13. Pin 39 may be driven externally by a TTL input signal four times the required E clock frequency. Pin 38 is to be grounded.

An RC network is not directly usable as a frequency source on pins 38 and 39. An RC network type TTL or CMOS oscillator will work well as long as the TTL or CMOS output drives the on-chip oscillator.

LC networks are not recommended to be used in place of the crystal.

If an external clock is used, it may not be halted for more than  $tpW_0L$ . The MC6802, MC6808 and MC6802NS are dynamic parts except for the internal RAM, and require the external clock to retain information.

#### MEMORY READY (MR)

MR is a TTL-compatible input signal controlling the stretching of E. Use of MR requires synchronization with the 4xf<sub>0</sub> signal, as shown in Figure 14. When MR is high, E will be in normal operation. When MR is low, E will be stretched integral numbers of half periods, thus allowing interface to slow memories. Memory Ready timing is shown in Figure 15.

MR should be tied high (connected directly to V<sub>CC</sub>) if not used. This is necessary to ensure proper operation of the part. A maximum stretch is  $t_{\rm CYC}$ .

### ENABLE (E)

This pin supplies the clock for the MPU and the rest of the system. This is a single-phase, TTL-compatible clock. This clock may be conditioned by a memory read signal. This is equivalent to  $\phi 2$  on the MC6800. This output is capable of driving one standard TTL load and 130 pF.

### VCC STANDBY (MC6802 ONLY)

This pin supplies the dc voltage to the first 32 bytes of RAM as well as the RAM Enable (RE) control logic. Thus, retention of data in this portion of the RAM on a power-up, power-down, or standby condition is guaranteed. Maximum current drain at VSB maximum is ISBB. For the MC6802NS this pin must be connected to VCC.

#### MPU INSTRUCTION SET

The instruction set has 72 different instructions. Included are binary and decimal arithmetic, logical, shift, rotate, load, store, conditional or unconditional branch, interrupt and stack manipulation instructions (Tables 2 through 6). The instruction set is the same as that for the MC6800.

### MPU ADDRESSING MODES

There are seven address modes that can be used by a programmer, with the addressing mode a function of both the type of instruction and the coding within the instruction. A summary of the addressing modes for a particular instruction can be found in Table 7 along with the associated instruction execution time that is given in machine cycles. With a bus frequency of 1 MHz, these times would be microseconds.

### ACCUMULATOR (ACCX) ADDRESSING

In accumulator only addressing, either accumulator A or accumulator B is specified. These are one-byte instructions.

### IMMEDIATE ADDRESSING

In immediate addressing, the operand is contained in the second byte of the instruction except LDS and LDX which have the operand in the second and third bytes of the instruction. The MPU addresses this location when it fetches the immediate instruction for execution. These are two- or three-byte instructions.

### DIRECT ADDRESSING

In direct addressing, the address of the operand is contained in the second byte of the instruction. Direct addressing allows the user to directly address the lowest 256 bytes in the machine, i.e., locations zero through 255. Enhanced execution times are achieved by storing data in these locations. In most configurations, it should be a random-access memory. These are two-byte instructions.

### EXTENDED ADDRESSING

In extended addressing, the address contained in the second byte of the instruction is used as the higher eight bits of the address of the operand. The third byte of the instruction is used as the lower eight bits of the address for the operand. This is an absolute address in memory. These are three-byte instructions.

### INDEXED ADDRESSING

In indexed addressing, the address contained in the second byte of the instruction is added to the index register's lowest eight bits in the MPU. The carry is then added to the higher order eight bits of the index register. This result is then used to address memory. The modified address is held in a temporary address register so there is no change to the index register. These are two-byte instructions.

### IMPLIED ADDRESSING

In the implied addressing mode, the instruction gives the address (i.e., stack pointer, index register, etc.). These are one-byte instructions.

### RELATIVE ADDRESSING

In relative addressing, the address contained in the second

byte of the instruction is added to the program counter's lowest eight bits plus two. The carry or borrow is then added to the high eight bits. This allows the user to address data within a range of -125 to +129 bytes of the present instruction. These are two-byte instructions.

## TABLE 2 - MICROPROCESSOR INSTRUCTION SET - ALPHABETIC SEQUENCE

| ABA | Add Accumulators                | CLR | Clear                    | PUL        | Pull Data                                                          |

|-----|---------------------------------|-----|--------------------------|------------|--------------------------------------------------------------------|

| ADC | Add with Carry                  | CLV | Clear Overflow           | ROL        | Rotate Left                                                        |

| ADD | Add                             | CMP | Compare                  | ROR        | Rotate Right                                                       |

| AND | Logical And                     | COM | Complement               | RTI        | Return from Interrupt                                              |

| ASL | Arithmetic Shift Left           | CPX | Compare Index Register   | RTS        | Return from Subroutine                                             |

| ASR | Arithmetic Shift Right          | DAA | Decimal Adjust           | SBA        | Subtract Accumulators                                              |

| BCC | Branch if Carry Clear           | DEC | Decrement                | SBC        | Subtract with Carry                                                |

| BCS | Branch if Carry Set             | DES | Decrement Stack Pointer  | SEC        | Set Carry                                                          |

| BEQ | Branch if Equal to Zero         | DEX | Decrement Index Register | SEI        | Set Interrupt Mask                                                 |

| BGE | Branch if Greater or Equal Zero |     | _                        | SEV        | Set Overflow                                                       |

| BGT | Branch if Greater than Zero     | EOR | Exclusive OR             | STA        | Store Accumulator                                                  |

| BHI | Branch if Higher                | INC | Increment                | STS        | Store Stack Register                                               |

| BIT | Bit Test                        | INS | Increment Stack Pointer  | STX        | Store Index Register                                               |

| BLE | Branch if Less or Equal         | INX | Increment Index Register | SUB        | Subtract                                                           |

| BLS | Branch if Lower or Same         | JMP | Jump                     | SWI        | Software Interrupt                                                 |

| BLT | Branch if Less than Zero        | JSR | Jump to Subroutine       |            | Transfer Accumulators                                              |

| BMI | Branch if Minus                 |     | •                        | TAB        |                                                                    |

| BNE | Branch if Not Equal to Zero     | LDA | Load Accumulator         | TAP        | Transfer Accumulators to Condition Code Reg. Transfer Accumulators |

| BPL | Branch if Plus                  | LDS | Load Stack Pointer       | TBA        | Transfer Accumulators Transfer Condition Code Reg. to Accumulator  |

| BRA | Branch Always                   | LDX | Load Index Register      | TPA<br>TST | Test                                                               |

| BSR | Branch to Subroutine            | LSR | Logical Shift Right      | TSX        | Transfer Stack Pointer to Index Register                           |

| BVC | Branch if Overflow Clear        | NEG | Negate                   | TXS        | Transfer Index Register to Stack Pointer                           |

| BVS | Branch if Overflow Set          | NOP | No Operation             |            | <u>-</u>                                                           |

| CBA | Compare Accumulators            |     | Inclusive OR Accumulator | WAI        | Wait for Interrupt                                                 |

| CLC | Clear Carry                     | ORA |                          |            |                                                                    |

| CLI | Clear Interrupt Mask            | PSH | Push Data                |            |                                                                    |

|     |                                 |     |                          |            |                                                                    |

TABLE 3 - ACCUMULATOR AND MEMORY INSTRUCTIONS

|                         |              |          |     |   |          |      | AD | DRES     | SING | МС | OE\$     |     |   |     |      |   | BOOLEAN/ARITHMETIC OPERATION               | COP       | IO. | col | Œ            | RE         |

|-------------------------|--------------|----------|-----|---|----------|------|----|----------|------|----|----------|-----|---|-----|------|---|--------------------------------------------|-----------|-----|-----|--------------|------------|

|                         |              | -        | MME | _ |          | IREC |    | -        | NDE) |    |          | XTN | D |     | PLIE | 0 | (All register labels                       |           |     | 3   |              | ·          |

| OPERATIONS              | MNEMONIC     | DP       |     | = | GP       | _    | _= | OP       | -    | =  | OP       | _   | = | OP  |      | = | refer to contents)                         | "         | '   | N Z | +            | +          |

| Add                     | ACDA         | 88       | 2   | 2 | 98       | 3    | 2  | 8A       | 5    | 2  | 88       | 4   | 3 |     |      |   | A • M • A                                  |           | •   | ٠,  |              | 1          |

| Add Acmites             | ADDB<br>ABA  | C8       | 2   | 2 | 08       | 3    | 5  | £8       | 5    | 2  | FB       | ٠   | 3 | 18  | 2    | , | 8 + M · B<br>A + B · A                     |           | :   |     |              | :          |

| Add with Carry          | ADCA         | 89       | 2   | 2 | 99       | 3    | 2  | A9       | 5    | 2  | B9       | 4   | 3 |     | •    |   | A · M · C · A                              |           |     |     |              | i          |

|                         | ADCB         | C9       | 2   | 2 | D9       | 3    | 2  | E9       | 5    | 2  | F9       | 4   | 3 |     |      |   | 8 + M + C -8                               |           | •   |     |              | 1          |

| And                     | ANDA         | 84<br>C4 | 2   | 2 | 94<br>D4 | 3    | 2  | A4       | 5    | 2  | 84<br>F4 | 4   | 3 |     |      |   | A·M·A<br>R·M·R                             |           | •   |     |              | R          |

| Bit Test                | AND8<br>BITA | 85       | 2   | 2 | 95       | 3    | 2  | E4<br>A5 | 5    | 2  | 85       | 4   | 3 |     |      |   | B·M·B<br>A·M                               |           | :   |     |              | R<br>R     |

| Dit Teat                | BITB         | C5       | 2   | 2 | 05       | 3    | 2  | E5       | 5    | 2  | F5       | 4   | 3 |     |      |   | в-м                                        |           | •   |     |              | R          |

| Clear                   | CLR          |          |     |   |          |      |    | 6F       | 7    | 2  | 7 F      | 6   | 3 |     |      |   | 00 · M                                     |           |     |     |              | R          |

|                         | CLRA         |          |     |   |          |      |    |          |      |    |          |     |   | 4f  | 2    | ! | 00 · A                                     |           |     |     |              | B          |

| Compare                 | CLAB         | 81       | 2   | 2 | 91       | 3    | 2  | AI       | 5    | 2  | 81       | 4   | 3 | 5F  | 2    | 1 | 00 ·B                                      |           | :   |     |              | R          |

| Compare                 | CMPB         | C1       | 2   | 2 | 01       | 3    | 2  | E1       | 5    | 2  | FI       | 4   | 3 |     |      |   | B M                                        | .         |     | :   |              | il         |

| Compare Acmitrs         | CBA          | -        |     |   | _        |      |    |          |      |    | 1        |     |   | 11  | 2    | 1 | A B                                        | ]•        | •   | :   | :            | :          |

| Camplement, 1's         | COM          | 1        |     |   |          |      |    | 63       | 7    | 2  | 73       | 6   | 3 |     |      |   | M · M                                      | •         | •   |     |              | R          |

|                         | COMA         | 1        |     |   |          |      |    |          |      |    |          |     |   | 43  | 2    | 1 | Ā · A                                      | 1.        | •   |     |              | R          |

| Complement, 2's         | COMB<br>NEG  | 1        |     |   | İ        |      |    | 60       | 7    | 2  | 70       | 6   | 3 | 53  | 2    | 1 | 8 · B<br>00 M · M                          |           | :   |     |              | R<br>Dic   |

| (Negate)                | NEGA         | 1        |     |   |          |      |    | 1 30     | ′    | 2  | l ′°     | •   | ٥ | 40  | 2    | 1 | 00 A - A                                   |           |     |     |              | ä          |

| ,                       | NEGB         | 1        |     |   |          |      |    |          |      |    | ]        |     |   | 50  | 2    | 1 | 00 8 -8                                    | 1.        | •   | :   | : 6          | D          |

| Decimal Adjust, A       | DAA          | 1        |     |   |          |      |    |          |      |    | 1        |     |   | 19  | 2    | 1 | Converts Binary Add of BCD Characters      | •         | •   | :   |              | : K        |

|                         |              | 1        |     |   |          |      |    |          |      |    | ١        | _   |   |     |      |   | into BCD Format                            | П         |     | . [ | ٦,           | $\sqrt{}$  |

| Decrement               | DEC<br>DECA  | 1        |     |   |          |      |    | 6A       | 7    | 2  | 7A       | 6   | 3 | 4.6 | 2    | 1 | M 1 · M<br>A 1 · A                         | :         | :   | :   |              | 욁          |

|                         | DECA         | 1        |     |   |          |      |    | ł        |      |    |          |     |   | 5A  | 2    | 1 | 8 1 -8                                     | !:        |     | :   | :            | 9          |

| Exclusive OR            | EGRA         | 88       | 2   | 2 | 98       | 3    | 2  | A8       | 5    | 2  | 88       | 4   | 3 | 371 |      |   | A⊕M -A                                     | •         |     | :1  | : [          | R.         |

|                         | EORB         | Ca       | 2   | 2 | 08       | 3    | 2  | E8       | 5    | 2  | F8       | 4   | 3 |     |      |   | B⊕M ·B                                     | •         | •   | :   |              | R .        |

| Increment               | INC          |          |     |   | l        |      |    | 60       | 7    | 2  | 7 C      | 6   | 3 |     |      |   | M + 1 - 14                                 | •         | •   |     | : (          | <u>s</u> ) |

|                         | INCA         |          |     |   | l        |      |    |          |      |    |          |     |   | 40  | 2    | 1 | A - 1 - A                                  |           | •   |     | 10           | <u></u>    |

| Load Acmit:             | LDAA         | 86       | 2   | 2 | 96       | 3    | 2  | Α6       | 5    | 2  | 86       | - 4 | 3 | 5C  | 2    | 1 | B + I · B<br>M · Δ                         |           | :   | :   | : (          | 5)<br>R    |

| COAU ACTION             | LDAB         | C6       | 2   | 2 | D6       | 3    | 2  | E 6      | 5    | 2  | F6       | 4   | 3 |     |      |   | M · B                                      | .         |     |     | Н            | R          |

| Or, Inclusive           | ORAA         | 8A       | 2   | 2 | 9.4      | 3    | 2  | AA       | 5    | 2  | ВА       | 4   | 3 | i   |      |   | A+M ·A                                     | i•i       | •   |     |              | R.         |

|                         | ORAB         | CA       | 2   | 2 | DA       | 3    | 2  | EA       | 5    | 2  | FA       | 4   | 3 |     |      |   | B+M -B                                     | •         | •   |     |              | R .        |

| Push Data               | PSHA         | l        |     |   | l        |      |    |          |      |    |          |     |   | 36  | 4    | 1 | A · MSP. SP 1 · SP                         | •         | •   |     |              | •          |

| Pull Data               | PSHB<br>PULA | l        |     |   | l        |      |    |          |      |    |          |     |   | 37  | 4    | 1 | B · MSP, SP I · SP<br>SP · 1 · SP, MSP · A |           | :   |     |              |            |

| run Data                | PULB         | l        |     |   | l        |      |    |          |      |    |          |     |   | 33  | 4    | i | SP + 1 - SP, MSP - B                       | 1.1       |     |     |              |            |

| Relate Left             | ROL          | l        |     |   |          |      |    | 69       | 2    | 2  | 79       | 6   | 3 |     |      |   | M)                                         | •         | •   | :   | : 0          | 0          |

|                         | ROLA         |          |     |   | 1        |      |    |          |      |    |          |     |   | 49  | 2    | 1 | ^ \ \_O ~ @#####_                          | •         | •   |     | : [0         | 6          |

|                         | ROLB         | 1        |     |   | 1        |      |    | ١        |      |    |          |     |   | 59  | 2    | 1 | B C 67 - 60                                | •         | •   |     |              | 9          |

| Rotate Right            | RORA         | l        |     |   |          |      |    | 66       | 7    | 2  | 76       | 6   | 3 | 46  | 2    | 1 | M -0 + 011111111                           |           | :   |     |              | 6          |

|                         | RORB         | l        |     |   |          |      |    |          |      |    |          |     |   | 56  | 2    | i | B C 67 - 60                                |           |     |     |              | 6          |

| Shift Left, Arithmetic  | ASL          | l        |     |   |          |      |    | 68       | 7    | 2  | 78       | 6   | 3 |     |      |   | M) +                                       |           | •   |     |              | 6          |

|                         | ASLA         | 1        |     |   |          |      |    | 1        |      |    |          |     |   | 48  | 2    | 1 | A} 0 + 0000000+0                           | •         | •   |     |              | Ð          |

|                         | ASLB         | 1        |     |   |          |      |    |          | ,    | ,  | ,,       |     | , | 58  | 2    | 1 | В С 67 60                                  | <b> •</b> | •   |     | : [9         | 9          |

| Shift Right, Arithmetic | ASR<br>ASRA  | 1        |     |   |          |      |    | 6/       | 7    | 2  | 11       | 6   | 3 | 47  | 2    | , | M)                                         | :         | :   |     | : (0<br>: (0 | 0          |

|                         | ASRB         | 1        |     |   |          |      |    |          |      |    |          |     |   | 57  | 2    | i | A - C - C - C - C                          |           |     |     |              | 8          |

| Shift Right, Logic      | LSR          | 1        |     |   |          |      |    | 64       | 7    | 2  | 74       | 6   | 3 |     | •    |   | M) -                                       | -         |     |     |              | 5          |

|                         | LSAA         | 1        |     |   |          |      |    |          |      |    |          |     |   | 44  | 2    | 1 | A} 0+CIIIII + C                            | •         | •   | А   | : (          | 6          |

|                         | LSAB         | 1        |     |   | l .      |      | _  | ١.       |      | _  | 1        |     |   | 54  | 2    | 1 | B) 67 60 C                                 | •         | •   |     |              | 6          |

| Store Acmitr            | AAT2<br>BAT2 |          |     |   | 97<br>D7 | 4    | 2  | A /      | 6    | 2  | B7       | 5   | 3 |     |      |   | A · M<br>B · M                             | :         | •   | .   |              | R          |

| Subtract                | SUBA         | 80       | 2   | 2 | 90       | 3    | 2  | A0       | 5    | 2  | 80       | 4   | 3 |     |      |   | B · M<br>A M · A                           |           | :   |     |              | R<br>1     |

| augmati.                | SUBB         | CO       |     | 2 | 00       | 3    | 2  | EO       | 5    | 2  | FO       | 4   | 3 |     |      |   | B M -B                                     |           |     | :   |              | :1         |

| Subtract Acmitrs.       | SBA          |          |     |   |          |      |    |          |      |    |          |     |   | 10  | 2    | 1 | A B · A                                    | •         | •   | ij  | :            | 1          |

| Subtr with Carry        | SBCA         | 82       | 2   | 2 | 92       | 3    | 2  | AZ       | 5    | 2  | 82       | 4   | 3 |     |      |   | A M C · A                                  | •         | •   |     | !            | :          |

|                         | SBCB         | CZ       | 2   | 2 | D2       | 3    | 2  | E2       | 5    | 2  | F2       | 4   | 3 | ١., | ,    |   | B M C - B                                  | •         | •   |     |              |            |

| Transfer Acmitis        | TAB<br>TBA   | 1        |     |   | 1        |      |    |          |      |    |          |     |   | 16  | 2    | 1 | A · B<br>B · A                             |           | :   |     |              | H H        |

| Test, Zero or Minus     | TST          | 1        |     |   | İ        |      |    | 60       | 7    | 2  | 70       | 6   | 3 | l " |      |   | M 00                                       |           | :   |     |              | H          |

|                         | TSTA         | 1        |     |   |          |      |    | -        |      |    | -        | -   | - | 40  | 2    | 1 | A 00                                       |           | •   | :   | : 1          | Я          |

|                         | TSTB         | 1        |     |   |          |      |    | l        |      |    |          |     |   | 50  | 2    | 1 | B - 00                                     | •         | •   |     |              | A          |

|                         |              | •        | _   |   | -        |      |    |          |      | _  |          |     |   |     |      |   |                                            | н         | ī   | N   | z ·          | ٧ĺ         |

### LEGEND:

- DP Dperation Code (Hexadecimal).

Number of MPU Cycles.

Number of Program Bytes.

Arithmetic Plus;

Arithmetic Minus.

- Boolean AND.

- MSP Contents of memory location pointed to be Stack Pointer.

Note - Accumulator addressing mode instructions are included in the column for IMPLIED addressing

### CONDITION CODE SYMBOLS:

- Half carry from bit 3,

- H Half Carry from bit 2,

Instruction mask

N Negative login bit 1

2 Zero (byte)

V Overflow, 2's complement

C Carry from bit 7

Reset Always

S Set Always

1 Test and set if true, cleared otherwise

Not Affected

+ Boolean Inclusive OR.

Boolean Exclusive OR.

Complement of M.

Transfer Into.

O Bit - Zero.

OO Byte - Zero.

TABLE 4 - INDEX REGISTER AND STACK MANIPULATION INSTRUCTIONS

|                       |          |     |     |   |    |     |     |    |     |    |      |     |   |    |      |    |                              | CO | ND | . cc | DE  | R   | G. |

|-----------------------|----------|-----|-----|---|----|-----|-----|----|-----|----|------|-----|---|----|------|----|------------------------------|----|----|------|-----|-----|----|

|                       |          | 16  | MME | D | D  | IRE | ÇT. | 1  | NDE | x  | E    | XTN | D | IN | IPLI | ED |                              | 5  | 4  | 3    | 2   | 1   | 0  |

| POINTER OPERATIONS    | MNEMONIC | OP  | ~   | = | OР | ~   | =   | OP | -   | == | OP   | ~   | = | OP | ~    | =  | BOOLEAN/ARITHMETIC OPERATION | н  | 1  | N    | z   | ٧   | C  |

| Compare Index Reg     | CPX      | 8 C | 3   | 3 | 9€ | 4   | 2   | AC | 6   | 2  | B.C. | 5   | 3 |    |      |    | XH - M, XL - (M + 1)         | •  | •  | 1    | П   | (8) | •  |

| Decrement Index Req   | DEX      |     |     |   |    | ļ   |     | į  | 1   |    |      |     |   | 09 | 4    | 1  | X - 1 - X                    | •  | •  | ٠    | 11  | •   | •  |

| Decrement Stack Potr  | DES      |     |     |   |    | 1   |     |    | 1   |    | -    |     |   | 34 | 4    | 1  | SP 1 · SP                    | •  | •  | ٠    | •   | •   | •  |

| Increment Index Reg   | INX      |     |     |   |    |     |     |    | 1   |    |      |     |   | 08 | 4    | 1  | X + 1 · X                    | •  | •  | ٠    | :   | •   | •  |

| Increment Stack Potr  | INS      |     |     |   |    |     |     |    | !   |    |      |     |   | 31 | 4    | 1  | SP + 1 · SP                  | •  | ٠  | -    | •   | •   | •  |

| Load Index Reg        | LDX      | C€  | 3   | 3 | DE | 4   | 2   | EE | 6   | 2  | FE   | 5   | 3 |    | i    |    | M · XH, {M + 1} · XL         | •  | •  | 9    |     | R   | •  |

| Load Stack Potr       | LDS      | 8E  | 3   | 3 | 9E | 4   | 2   | AE | 6   | 2  | BE   | 5   | 3 |    | ĺ    |    | M · SPH, (M + 1) · SPL       |    |    | (9)  |     | R   |    |

| Store Index Reg       | STX      |     |     | l | DF | 5   | 2   | EF | 7   | 2  | FF   | 6   | 3 | İ  |      |    | XH -M, XL -(M+1)             |    |    | (9)  |     |     |    |

| Store Stack Potr      | STS      |     |     | l | 9F | 5   | 2   | AF | 7   | 2  | BF   | 6   | 3 |    |      |    | SPH + M, SPL - (M + 1)       | •  | •  | (9)  | 133 | R   | •  |

| Indx Reg - Stack Potr | TXS      |     |     |   |    |     |     |    |     | í  |      |     |   | 35 | 4    | 1  | X 1 · SP                     | •  | ٠  | •    | •   | •   | •, |

| Stack Potr - Indx Reg | TSX      |     |     |   |    |     |     |    |     | Ĺ  |      |     |   | 30 | 4    | 1  | SP + 1 - X                   |    | •  | ٠    | •   | ٠   | •  |

### TABLE 5 - JUMP AND BRANCH INSTRUCTIONS

|                          |          |     |     |     |    |     |   |     |     |   |    |      |     |     |                           |   | CON | D. C | ODE    | REG |   |

|--------------------------|----------|-----|-----|-----|----|-----|---|-----|-----|---|----|------|-----|-----|---------------------------|---|-----|------|--------|-----|---|

|                          |          | RE  | LAT | IVE | 1  | NDE | X | E   | XTN | D | IN | PLIE | 0   |     |                           | 5 | 4   | 3    | 2      | 1   |   |

| OPERATIONS               | MNEMONIC | OP  | ~   | #   | OP | ~   | # | OP  | ~   |   | 0P | ~    | #   |     | BRANCH TEST               | Н | 1   | N    | Z      | ٧   | ı |

| Branch Always            | BRA      | 20  | 4   | 2   |    |     |   |     |     |   |    |      |     |     | Nane                      | • | •   | •    | •      | •   | 1 |

| Branch If Carry Clear    | BCC      | 24  | 4   | 2   |    |     |   |     |     |   |    |      |     |     | C = 0                     | • | •   | •    | •      | •   |   |

| Branch If Carry Set      | BCS      | 25  | 4   | 2   | l  |     |   |     |     |   |    |      |     |     | C = 1                     | • | •   | •    | •      | •   | ı |

| Branch It = Zero         | BEQ      | 27  | 4   | 2   |    | Į   |   |     |     |   |    |      |     |     | Z = 1                     | • | •   | •    | •      | •   | 1 |

| Branch If ≥ Zero         | BGE      | 2 C | 4   | 2   |    | 1   |   |     | 1   |   |    |      |     |     | N ⊕ V = 0                 | • | •   | •    | •      | •   |   |

| Branch If > Zero         | BGT      | 2 E | 4   | 2   |    |     |   |     | i   |   |    |      |     |     | $Z + (N \oplus V) = 0$    | • | •   |      | •      | •   |   |

| Branch If Higher         | ВНІ      | 22  | 4   | 2   |    |     |   |     |     |   |    |      | ļ   | l   | C + Z = 0                 | • | •   | •    | . •    | •   |   |

| Branch If ≤ Zero         | BLE      | 2 F | 4   | 2   | 1  |     | ŀ |     | l   |   | ĺ  |      | Ì   |     | Z + (N ⊕ V) = 1           | • | •   | •    |        | •   |   |

| Branch It Lower Or Same  | BLS      | 23  | 4   | 2   | ļ  |     | Į |     | İ   |   |    |      | 1   | ŀ   | C + Z = 1                 | • | •   | •    | . •    | •   |   |

| Branch If < Zero         | BLT      | 2 D | 4   | 2   |    |     | ĺ |     |     |   |    | ŀ    |     |     | N ⊕ V = 1                 | • | •   | •    |        | •   |   |

| Branch If Minus          | BM)      | 28  | 4   | 2   | ŀ  | ļ   | 1 |     |     |   | İ  | ŀ    |     | l   | N = 1                     | • |     | •    |        | •   | 1 |

| Branch II Not Equal Zero | BNE      | 26  | 4   | 2   | 1  | 1   | 1 | l   |     |   | i  |      |     | i   | Z = 0                     | • | •   | •    | ٠.     | •   |   |

| Branch II Overflow Clear | BVC      | 28  | 4   | 2   | l  |     | 1 |     |     |   |    |      |     | ļ   | V = 0                     | • | •   |      | ٠.     | •   |   |

| Branch If Overflow Set   | BVS      | 29  | 4   | 2   |    |     | 1 |     |     | 1 | 1  | l    |     | 1   | V = 1                     | • | ٠   | •    | •      | •   |   |

| Branch II Plus           | BPL      | 2 A | 4   | 2   | -  |     |   |     |     | ļ | 1  | 1    |     | 1   | N = 0                     | • | •   | •    | į •    |     | i |

| Branch To Subroutine     | BSR      | 8 D | 8   | 2   |    |     |   |     | 1   |   |    |      |     | 1   |                           | • | •   | •    |        | •   | İ |

| Jump                     | JMP      | Ī   | ,   |     | 6E | 4   | 2 | 7 E | 3   | 3 |    |      | į . | 1   | See Special Operations    | • | •   | •    | •      | •   |   |

| Jump To Subroutine       | JSR      |     | ì   | 1   | AD | 8   | 2 | BD  | 9   | 3 |    |      | !   | )   | (Figure 16)               | • | ٠   | •    | •      | j • |   |

| No Operation             | NOP      |     | l   |     |    | 1   |   | l   |     |   | 01 | 2    | 1   |     | Advances Prog. Cntr. Only | • | •   | •    | ્ર•    | į • |   |

| Return From Interrupt    | RTI      |     |     |     |    | 1   |   | l   |     |   | 3B | 10   | 1   |     |                           |   |     | - (  | (10) - |     | - |

| Return From Subroutine   | RTS      | 1   | 1   |     |    | 1   | 1 |     | ĺ   |   | 39 | 5    | 1   | 1   |                           | • | . • | •    |        | •   | 1 |

| Software Interrupt       | SWI      |     |     |     | İ  | 1   |   |     | 1   |   | 3F | 12   | 1   | 1.2 | See Special Operations    | • |     | į •  | •      |     |   |

| Wait for Interrupt       | WAI      | 1   |     | 1   | 1  | i i | 1 | 1   |     | 1 | 3E | 9    | 1   | 1 3 | (Figure 16)               | • | (0) | ۱•   |        |     |   |

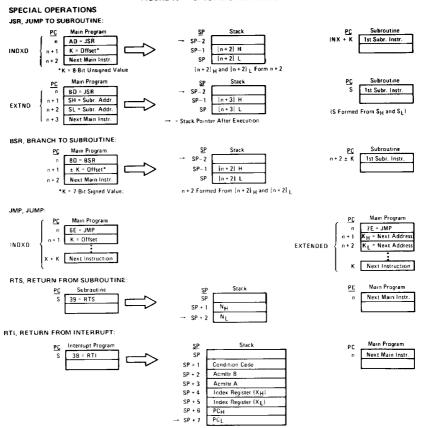

### FIGURE 16 - SPECIAL OPERATIONS

TABLE 6 - CONDITION CODE REGISTER MANIPULATION INSTRUCTIONS

|                      |          |    |      |     |                   |   | CON | D. CO | DDE      | REG. |     |

|----------------------|----------|----|------|-----|-------------------|---|-----|-------|----------|------|-----|

|                      |          | IM | PLIE | D   |                   | 5 | 4   | 3     | 2        | 1    | 0   |

| OPERATIONS           | MNEMONIC | OP | ~    | =   | BOOLEAN OPERATION | н | 1   | N     | z        | ٧    | C   |

| Clear Carry          | CLC      | ос | 2    | 1   | 0 · C             | • | •   | •     | •        | •    | 1   |

| Clear Interrupt Mask | CLI      | DE |      | 1   | 0 -1              | • | R   | •     | •        | •    | ١.  |

| Clear Overflow       | CLV      | OA | 2    | 1   | 0 - A             | • | •   | •     | •        | R    | ١.  |

| Set Carry            | SEC      | 00 | 2    | 3   | 1 - C             | • | •   | •     | •        | •    | 1 : |

| Set Interrupt Mask   | SEI      | 0F | 2    | . 1 | 1 •1              | • | S   | •     | •        | •    | ١.  |

| Set Overflow         | SEV      | 90 | 2    | 1   | 1 + V             | • | •   | •     |          | ls   | ١.  |

| Acmitr A → CCR       | TAP      | 06 | 2    | 1   | A · CCR           | _ | _   | —(1   | <u> </u> |      | _   |

| CCR + Acmltr A       | TPA      | 07 | 2    | 1   | CCR - A           | • | •   | •     |          | •    | 1 1 |

| CONDITION CODE REGISTER NOTES: | (Bit set if test is true and cleared otherwise |

|--------------------------------|------------------------------------------------|

|                                |                                                |

| 1 | (Bit V) | Test: Result = 10000000?                                                 | ,  | (BILLIA) | test: aidu dir di most sidumesur (mai nite - 1 -                  |

|---|---------|--------------------------------------------------------------------------|----|----------|-------------------------------------------------------------------|

| 2 | (Bit C) | Test: Result # 000000000?                                                | 8  | (Bit V)  | Test: 2's complement overflow from subtraction of MS bytes?       |

| 3 | (Bit C) | Test: Decimal value of most significant BCD Character greater than nine? | 9  | (Bit N)  | Test: Result less than zero? (Bit 15 = 1)                         |

|   |         | (Not cleared if previously set !                                         | 10 | (AII)    | Load Condition Code Register from Stack. (See Special Operations) |

| 4 | (Bit V) | Test: Operand = 10000000 prior to execution?                             | 11 | (Bit I)  | Set when interrupt occurs. If previously set, a Non-Maskable      |

| 5 | (Bit VI | Test: Operand = 01111111 prior to execution?                             |    |          | Interrupt is required to exit the wait state.                     |

| 6 | (Bit V) | Test: Set equal to result of N⊕C after shift has occurred.               | 12 | (AII)    | Set according to the contents of Accumulator A.                   |

|   |         |                                                                          |    |          |                                                                   |

TABLE 7 — INSTRUCTION ADDRESSING MODES AND ASSOCIATED EXECUTION TIMES (Times in Machine Cycle)

|            | (Dual Operand) | ACCX | Immediate | Direct | Extended | Indexed | Implied | Relative |            | (Dual Operand) | ACCX | Immediate | Direct | Extended | Indexed | Implied |

|------------|----------------|------|-----------|--------|----------|---------|---------|----------|------------|----------------|------|-----------|--------|----------|---------|---------|

| ABA        |                | •    | • 2       | 3      | 4        | 5       | 2       | •        | INC<br>INS |                | 2    | •         | •      | 6        | 7       | 4       |

| ADC<br>ADD | x              | :    | 2         | 3      | 4        | 5       | :       | :        | INX        |                | :    | :         |        |          |         | 4       |

| AND        | x              | :    | 2         | 3      | 4        | 5       |         |          | JMP        |                | •    | •         | •      | 3        | 4       | •       |

| ASL        | ^              | 2    | •         | •      | 6        | 7       | •       | •        | JSR        |                | •    | •         | •      | 9        | 8       | •       |

| ASR        |                | 2    | •         | •      | 6        | 7       | •       | •        | LDA        | x              | •    | 2         | 3.     | 4        | 5       | •       |

| BCC        |                | •    | •         | •      | •        | •       | •       | 4        | LDS        |                | •    | 3.        | 4      | 5<br>5   | 6<br>6  | •       |

| BCS        |                | •    | •         | •      | •        | •       | •       | 4        | LDX<br>LSR |                | 2    | •         | 4      | 6        | 7       | :       |

| BEA<br>BGE |                | •    | :         | :      | :        | :       | :       | 4        | NEG        |                | 2    | :         | :      | 6        | 7       |         |

| BGT        |                | :    | :         | :      | :        | :       |         | 4        | NOP        |                |      |           | •      | •        | •       | 2       |

| ВНІ        |                |      | •         | •      | •        |         | •       | 4        | ORA        | ×              | •    | 2         | 3      | 4        | 5       | •       |

| BIT        | ×              | •    | 2         | 3      | 4        | 5       | •       | •        | PSH        |                | •    | •         | •      | •        | •       | 4       |

| BLE        |                | •    | •         | •      | •        | •       | •       | 4        | PUL        |                | •    | •         | •      | •        | 7       | 4       |

| BLS        |                | •    | •         | •      | •        | •       | •       | 4        | ROL<br>ROR |                | 2    | :         | :      | 6<br>6   | 7       | :       |

| BLT<br>BMI |                | •    | •         | •      | •        | •       | :       | 4        | RTI        |                | -    | :         | :      | •        |         | 10      |

| BNE        |                | •    | :         | •      | :        | :       | :       | 4        | RTS        |                |      |           |        | •        |         | 5       |

| BPL        |                | •    | •         |        |          |         |         | 4        | SBA        |                | •    | •         | •      |          | •       | 2       |

| BRA        |                | •    | •         | •      | •        | •       | •       | 4        | SBC        | x              | •    | 2         | 3      | 4        | 5       | •       |

| BSR        |                | •    | •         | •      | •        | •       | •       | 8        | SEC        |                | •    | •         | •      | •        | •       | 2       |

| BVC        |                | •    | •         | •      | •        | •       | •       | 4        | SEI        |                | •    | •         | •      | •        | •       | 2       |

| BVS        |                | •    | •         | •      | •        | •       | •       | 4        | SEV<br>STA | ×              | •    | •         | 4      | 5        | 6       | •       |

| CBA        |                | •    | •         | •      | •        | •       | 2       | :        | STS        | *              | :    | :         | 5      | 6        | 7       | :       |

| CLC        |                | :    | :         | •      | •        | :       | 2       | :        | STX        |                |      |           | 5      | 6        | 7       | •       |

| CLR        |                | 2    | :         | :      | 6        | 7       | •       | :        | SUB        | ×              | •    | 2         | 3      | 4        | 5       | •       |

| CLV        |                | •    | •         |        | •        |         | 2       | •        | SWI        |                | •    | •         | •      | •        | •       | 12      |

| CMP        | ×              | •    | 2         | 3      | 4        | 5       | •       | •        | TAB        |                | •    | •         | •      | •        | •       | 2       |

| COM        |                | 2    | •         | •      | 6        | 7       | •       | •        | TAP        |                | •    | •         | •      | •        | •       | 2       |

| CPX        |                | •    | 3         | 4      | 5        | 6       | •       | •        | TBA<br>TPA |                | •    | •         | •      | •        | :       | 2       |

| DAA        |                | •    | •         | •      | 6        | 7       | 2       | •        | †PA<br>TST |                | 2    | :         | :      | 6        | 7       | •       |

| DEC<br>DES |                | 2    | :         | •      | 6        |         | 4       | :        | TSX        |                | •    | :         | :      | •        |         | 4       |

| DEX        |                | •    | :         | :      | :        | :       | 4       | :        | TSX        |                | •    |           | •      | •        | •       | 4       |

| EOR        | ×              | •    | 2         | 3      | 4        | 5       | •       | •        | WAI        |                | •    | •         | •      | •        | •       | 9       |

NOTE Interrupt time is 12 cycles from the end of the instruction being executed, except following a WAI instruction. Then it is 4 cycles.

Table 8 provides a detailed description of the information present on the address bus, data bus, valid memory address line (VMA), and the read/write line (R/ $\overline{W}$ ) during each cycle for each instruction.

This information is useful in comparing actual with expected results during debug of both software and hardware

as the control program is executed. The information is categorized in groups according to addressing modes and number of cycles per instruction. (In general, instructions with the same addressing mode and number of cycles execute in the same manner; exceptions are indicated in the table.)

### TABLE 8 - OPERATIONS SUMMARY

| Address Mode and Instructions | Cycles   | Cycle | VMA<br>Line | Address Bus                            | R/W<br>Line | Data Bus                        |

|-------------------------------|----------|-------|-------------|----------------------------------------|-------------|---------------------------------|

| IMMEDIATE                     |          |       |             |                                        |             |                                 |

| ADC EOR                       | 1        | 1     | 1           | Op Code Address                        | 1           | Op Code                         |

| ADD LDA<br>AND ORA            | 2        | 2     | 1           | Op Code Address + 1                    | 1           | Operand Data                    |

| BIT SBC                       | *        |       |             |                                        |             |                                 |

| CMP SUB                       | ļ        |       |             |                                        |             |                                 |

| CPX<br>LDS                    |          | 1     | 1           | Op Code Address                        | 1           | Op Code                         |

| LOX                           | 3        | 2     | 1           | Op Code Address + 1                    | 1           | Operand Data (High Order Byte)  |

|                               | <u> </u> | 3     | 1           | Op Code Address + 2                    | 1           | Operand Data (Low Order Byte)   |

| DIRECT                        | ,··      |       | _           |                                        |             | ·-                              |

| ADC EOR<br>ADD LDA            |          | 1     | 1           | Op Code Address                        | 1           | Op Code                         |

| AND ORA                       | 3        | 2     | 1           | Op Code Address + 1                    | 1           | Address of Operand              |

| BIT SBC<br>CMP SUB            | 1        | 3     | 1           | Address of Operand                     | 1           | Operand Data                    |

| CPX                           | <b> </b> | 1     | 1           | Op Code Address                        | 1           | Op Code                         |

| LDS<br>LDX                    | 4        | 2     | 1           | Op Code Address + 1                    | 1           | Address of Operand              |

| LUX                           | -        | 3     | 1           | Address of Operand                     | 1           | Operand Data (High Order Byte)  |

|                               |          | 4     | 1           | Operand Address + 1                    | 1           | Operand Data (Low Order Byte)   |

| STA                           |          | 1     | 1           | Op Code Address                        | 1           | Op Code                         |

|                               | 4        | 2     | 1           | Op Code Address + 1                    | 1           | Destination Address             |

|                               |          | 3     | 0           | Destination Address                    | 1           | Irrelevant Data (Note 1)        |

|                               |          | 4     | 1           | Destination Address                    | 0           | Data from Accumulator           |

| STS                           |          | 1     | 1           | Op Code Address                        | 1           | Op Code                         |

| STX                           |          | 2     | 1           | Op Code Address + 1                    | 1           | Address of Operand              |

|                               | 5        | 3     | 0           | Address of Operand                     | 1           | Irrelevant Data (Note 1)        |

|                               |          | 4     | 1           | Address of Operand                     | 0           | Register Data (High Order Byte) |

|                               |          | 5     | 1           | Address of Operand + 1                 | 0           | Register Data (Low Order Byte)  |

| INDEXED                       |          |       |             |                                        |             |                                 |